Rev. 1.10

56

November 26, 2019

Rev. 1.10

57

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

Input/Output Ports

Holtek microcontrollers offer considerable flexibility on their I/O ports. With the input or output

designation of every pin fully under user program control, pull-high selections for all ports and

wake-up selections on certain pins, the user is provided with an I/O structure to meet the needs of a

wide range of application possibilities.

The device provides bidirectional input/output lines labeled with port names PA~PE. These I/O

ports are mapped to the RAM Data Memory with specific addresses as shown in the Special Purpose

Data Memory table. All of these I/O ports can be used for input and output operations. For input

operation, these ports are non-latching, which means the inputs must be ready at the T2 rising edge

of instruction "MOV A, [m]", where m denotes the port address. For output operation, all the data is

latched and remains unchanged until the output latch is rewritten.

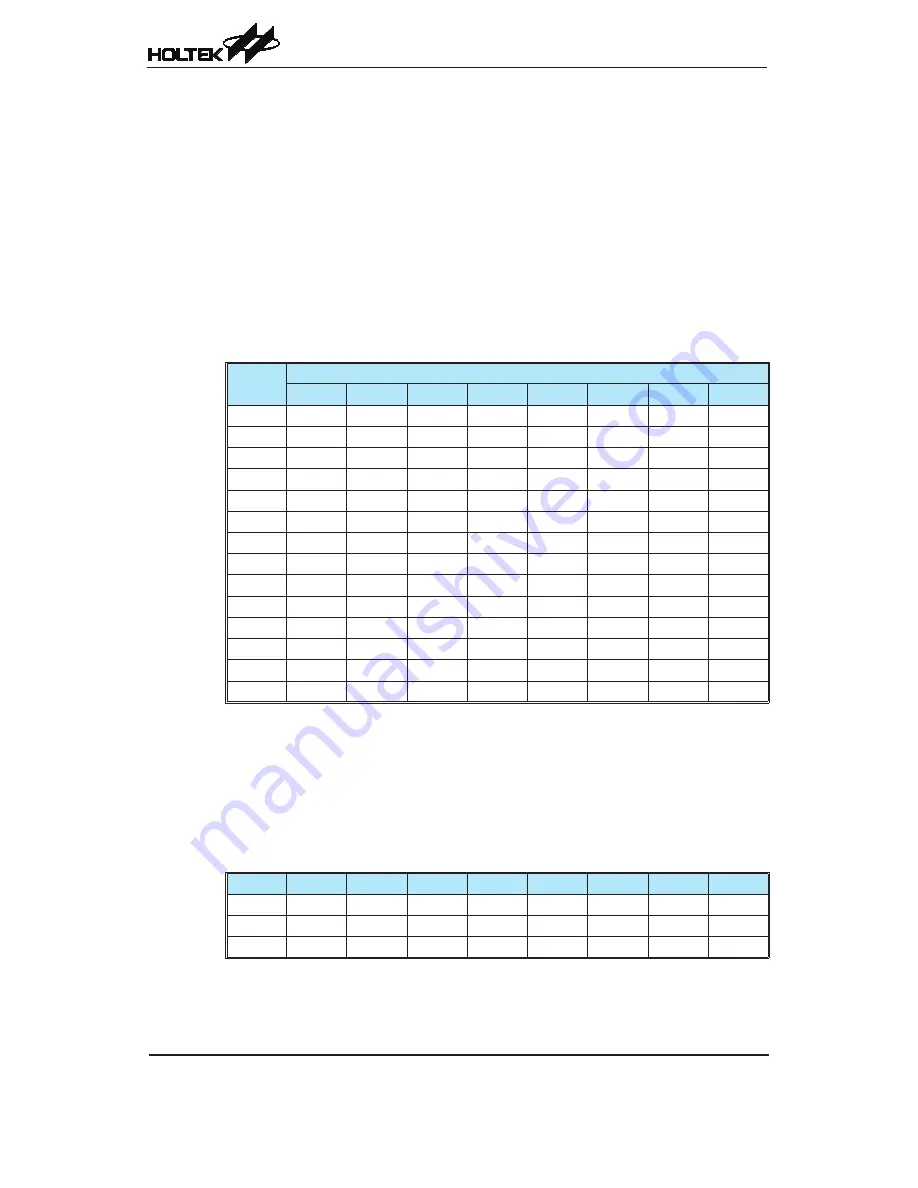

I/O Register List

Register

Name

Bit

7

6

5

4

3

2

1

0

PAWU

PAWU7

PAWU6

PAWU5

PAWU4

PAWU3

PAWU2

PAWU1

PAWU0

PAPU

PAPU7

PAPU6

PAPU5

PAPU4

PAPU3

PAPU2

PAPU1

PAPU0

PA

PA7

PA6

PA5

PA4

PA3

PA2

PA1

PA0

PAC

PAC7

PAC6

PAC5

PAC4

PAC3

PAC2

PAC1

PAC0

PXWU

—

PELWU

PDHWU PDLWU PCHWU PCLWU

PBHWU

PBLWU

PXPU

—

PELPU

PDHPU

PDLPU

PCHPU

PCLPU

PBHPU

PBLPU

PB

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

PBC

PBC7

PBC6

PBC5

PBC4

PBC3

PBC2

PBC1

PBC0

PC

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

PCC

PCC7

PCC6

PCC5

PCC4

PCC3

PCC2

PCC1

PCC0

PD

PD7

PD6

PD5

PD4

PD3

PD2

PD1

PD0

PDC

PDC7

PDC6

PDC5

PDC4

PDC3

PDC2

PDC1

PDC0

PE

—

—

—

—

—

—

PE1

PE0

PEC

—

—

—

—

—

—

PEC1

PEC0

Pull-high Resistors

Many product applications require pull-high resistors for their switch inputs usually requiring the

use of an external resistor. To eliminate the need for these external resistors, all I/O pins, when

configured as an input have the capability of being connected to an internal pull-high resistor. These

pull-high resistors are selected using registers PAPU

and PXPU, and are implemented using weak

PMOS transistors.

PAPU Register

Bit

7

6

5

4

3

2

1

0

Name

PAPU7

PAPU6

PAPU5

PAPU4

PAPU3

PAPU2

PAPU1

PAPU0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7~0

PAPU7~PAPU0:

Port A bit 7 ~ bit 0 Pull-high Control

0: Disable

1: Enable