Rev. 1.10

10

November 26, 2019

Rev. 1.10

11

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

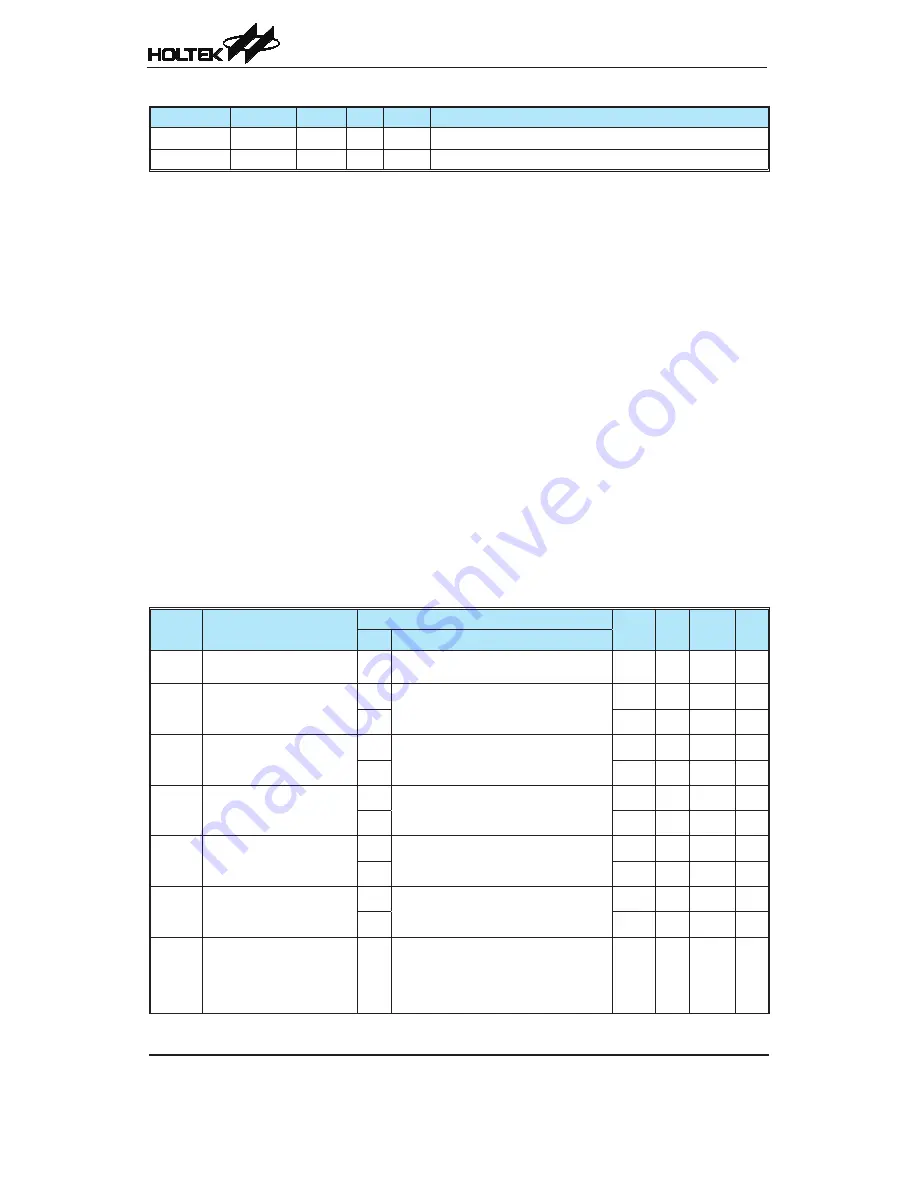

Pin Name

Function

OPT

I/T

O/T

Description

V33O

V33O

—

—

PWR 3.3V regulator output

VSS

VSS

—

PWR

—

Ground

Note: I/T: Input type;

O/T: Output type

OP: Optional by configuration option (CO) or register option

PWR: Power;

CO: Configuration option

ST: Schmitt Trigger input;

CMOS: CMOS output

Absolute Maximum Ratings

Supply Voltage

................................................................................................

V

SS

−0.3V to V

SS

+6.0V

Input Voltage

..................................................................................................V

SS

−

0.3V to V

DD

+0.3V

Storage Temperature

....................................................................................................

-50˚C to 125˚C

Operating Temperature

..................................................................................................

-40˚

C to 85

˚

C

I

OH

Total ..................................................................................................................................

-100mA

I

OL

Total ................................................................................................................................... 150mA

Total Power Dissipation

........................................................................................................

500mW

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum

Ratings" may cause substantial damage to these devices. Functional operation of these devices at

other conditions beyond those listed in the specification is not implied and prolonged exposure to

extreme conditions may affect devices reliability.

D.C. Characteristics

Ta= 25°C

Symbol

Parameter

Test Conditions

Min. Typ. Max. Unit

V

DD

Conditions

V

DD

Operating Voltage

(HIRC OSC)

─

f

SYS

=12MHz

3.3

—

5.5

V

I

DD1

Operating Current

(HIRC OSC, f

SYS

=f

H

,

f

S

=f

SUB

=f

LIRC

)

3V No load, f

H

=12MHz, WDT enable

USB disable, LVR enable

—

2.2

3.3

mA

5V

—

5.0

7.5

mA

I

DD2

Operating Current

(LIRC OSC, f

SYS

=f

L

=f

LIRC

,

f

S

=f

SUB

=f

LIRC

)

3V No load, WDT enable, f

LIRC

=32K,

Clear CLK_ADJ (SYSC.7=0)

USB disable, LVR enable

─

35

70

μA

5V

—

70

100

μA

I

DD3

Operating Current

(HIRC OSC, f

SYS

=f

H

,

f

S

=f

SUB

=f

LIRC

)

3V No load, f

H

=12MHz, WDT enable,

USB enable, V33O on, LVR enable

—

4.8

10

mA

5V

—

11

16

mA

I

STB1

Standby Current (Idle 0)

(HIRC OSC, f

SYS

=off,

f

S

=f

SUB

=f

LIRC

)

3V No load, system HALT, WDT enable,

f

SYS

=12MHz off (FSYSON=0),

Clear CLK_ADJ (SYSC.7=0)

—

1.5

3.0

μA

5V

—

3.0

6.0

μA

I

STB2

Standby Current (Sleep 0)

(HIRC OSC, f

SYS

=off,

f

S

=f

SUB

=f

LIRC

)

3V No load, system HALT, WDT disable,

f

SYS

=12MHz,

Clear CLK_ADJ (SYSC.7=0)

—

0.1

1

μA

5V

—

0.3

2

μA

I

SUS1

Suspend Current (Sleep 0)

(HIRC OSC, f

SYS

=off,

f

S

=f

SUB

=f

LIRC

)

5V

No load, system HALT, WDT disable,

LVR disable

USB transceiver, 3.3V Regulator on,

clr SUSP2 (UCC.4) and clr RCTRL

(UCC.7),Clear CLK_ADJ (SYSC.7=0)

—

330

400

μA