Rev. 1.10

52

November 26, 2019

Rev. 1.10

53

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

Software Reset Control

The devices provide the ability to control the MCU reset function enable or not by software option.

This function is managed by the FSWRST bit in the FRCR register.

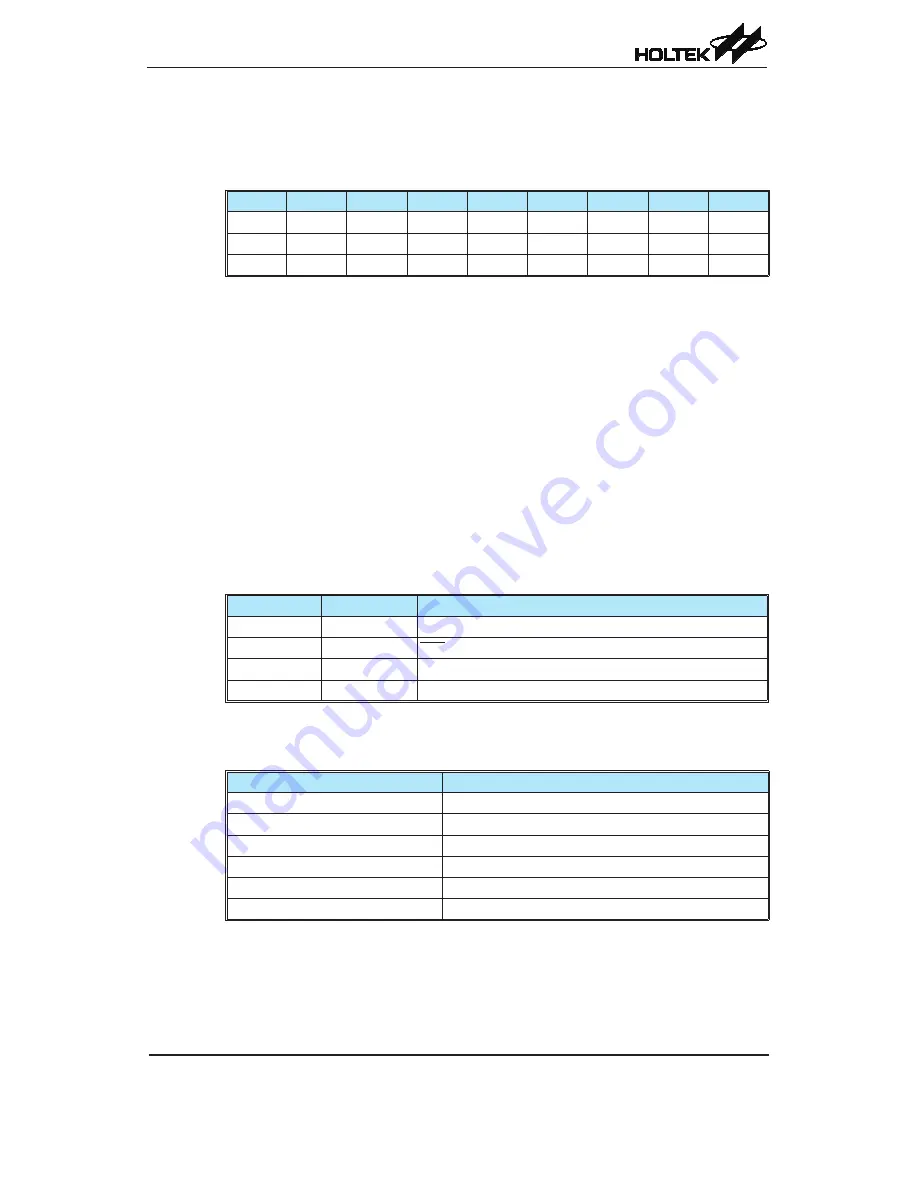

• FRCR Register

Bit

7

6

5

4

3

2

1

0

Name

—

—

—

FSWRST

—

—

—

CLWB

R/W

—

—

—

R/W

—

—

—

R/W

POR

—

—

—

0

—

—

—

0

Bit 7~5

Unimplemented, read as "0"

Bit 4

FSWRST:

Software Reset MCU control bit

0: MCU reset

enable

1: MCU reset disable (except power on reset)

This control bit is used to setup the reset action of MCU when there is a reset signal

detected by the USB SIE. If this bit is set to "0", the MCU reset will happen and if this

bit is set to "1", then the reset signal will be bypassed, the MCU will not be reset. Note

that the power on reset will not be controlled by the FSWRST bit.

Bit 3~1

unimplemented, read as "0"

Bit 0

CLWB:

Flash Program memory Write buffer clear control bit

Described

elsewhere

Reset Initial Conditions

The different types of reset described affect the reset flags in different ways. These flags, known

as PDF and TO are located in the status register and are controlled by various microcontroller

operations, such as the SLEEP or IDLE Mode function or Watchdog Timer. The reset flags are

shown in the table:

TO

Reset Conditions

0

0

Power-on reset

u

u

RES, LVR or USB reset during Normal or SLOW Mode operation

1

u

WDT time-out reset during Normal or SLOW Mode operation

1

1

WDT time-out reset during IDLE or SLEEP Mode operation

Note: "u" stands for unchanged

The following table indicates the way in which the various components of the microcontroller are

affected after a power-on reset occurs.

Item

Condition after Reset

Program Counter

Reset to zero

Interrupts

All interrupts will be disabled

WDT

Clear after reset, WDT begins counting

Timer/Event Counter

Timer Counter will be turned off

Input/Output Ports

I/O ports will be setup as inputs

Stack Pointer

Stack Pointer will point to the top of the stack