Rev. 1.10

98

November 26, 2019

Rev. 1.10

99

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

Interrupts

Interrupts are an important part of any microcontroller system. When an external event or an

internal function such as a Timer Module requires microcontroller attention, their corresponding

interrupt will enforce a temporary suspension of the main program allowing the microcontroller to

direct attention to their respective needs. The device contains several external interrupt and internal

interrupts functions. The external interrupt is generated by the action of the external INTn pin, while

the internal interrupts are generated by various internal functions such as TMs,

LVD

, SIM

and USB.

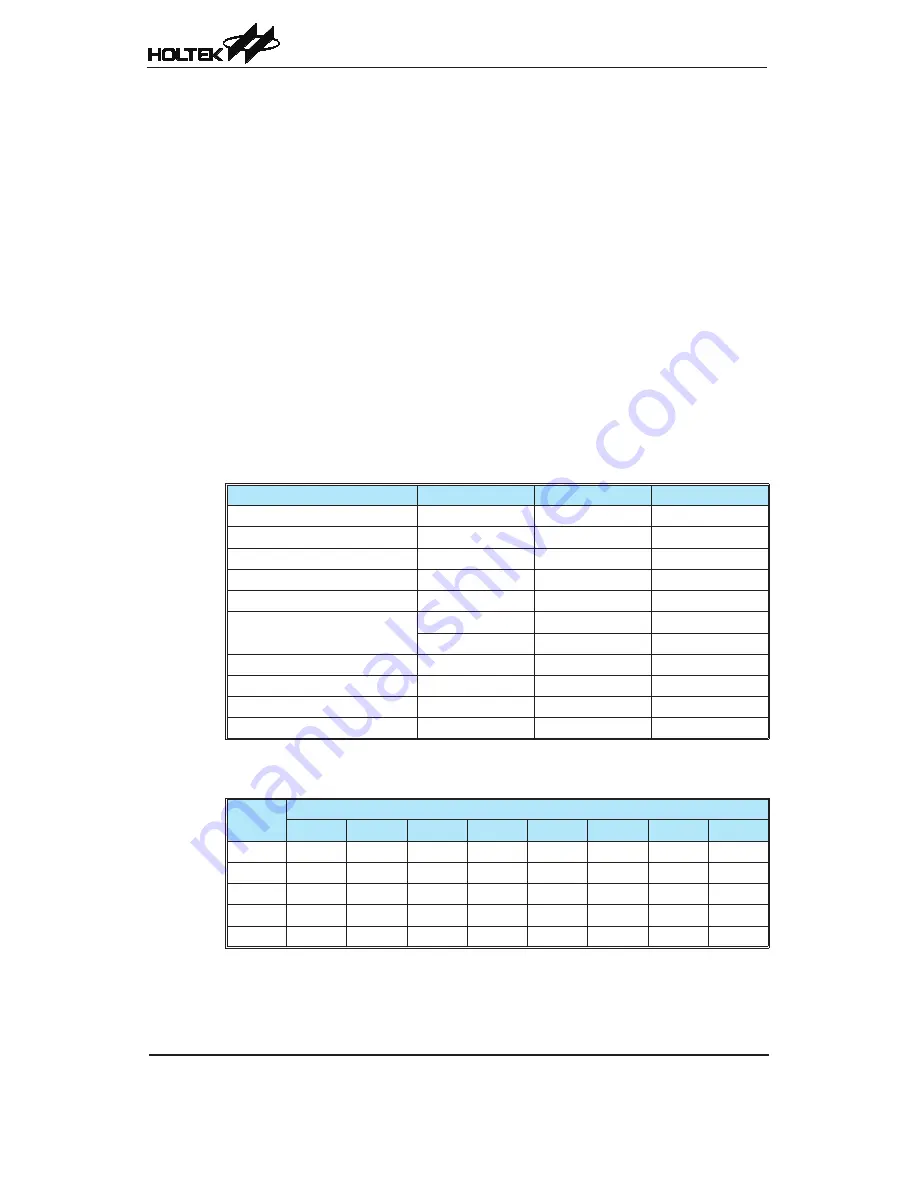

Interrupt Registers

Overall interrupt control, which basically means the setting of request flags when certain

microcontroller conditions occur and the setting of interrupt enable bits by the application program,

is controlled by a series of registers, located in the Special Purpose Data Memory, as shown in the

accompanying table. The first is the INTC0~INTC2 registers which setup the primary interrupts, the

second is the MFI0 register which setup the Multi-function interrupts.

Finally there is an INTEG

register to setup the external interrupt trigger edge type.

Each register contains a number of enable bits to enable or disable individual registers as well as

interrupt flags to indicate the presence of an interrupt request. The naming convention of these

follows a specific pattern. First is listed an abbreviated interrupt type, then the (optional) number of

that interrupt followed by either an "E" for enable/disable bit or "F" for request flag.

Function

Enable Bit

Request Flag

Notes

Global

EMI

—

—

INTn Pin

INTnE

INTnF

n=0~1

Multi-function

MF0E

MF0F

—

SIM

SIME

SIMF

—

LVD

LVE

LVF

—

TM

TnPE

TnPF

n=0~1

TnAE

TnAF

n=0~1

USB SIE

USBE

USBF

—

USB Setup Token

USTE

USTF

—

USB Endpoint 0 IN Token

UITE

UITF

—

USB Endpoint 0 OUT Token

UOTE

UOTF

—

Interrupt Register Bit Naming Conventions

Interrupt Register Contents

Register

Name

Bit

7

6

5

4

3

2

1

0

INTEG

—

—

—

—

INT1S1

INT1S0

INT0S1

INT0S0

INTC0

—

USBF

INT1F

INT0F

USBE

INT1E

INT0E

EMI

INTC1

—

UOTF

UITF

USTF

—

UOTE

UITE

USTE

INTC2

—

LVF

SIMF

MF0F

—

LVE

SIME

MF0E

MFI0

T1AF

T1PF

T0AF

T0PF

T1AE

T1PE

T0AE

T0PE