Page 14

RF65

Tel: +86-755-82973805 Fax: +86-755-82973550 E-mail: sales@hoperf.com http://www.hoperf.com

ADVANCED COMMUNICATIONS & SENSING

DATASHEET

TS_FEI

FEI sampling time

Receiver is ready

-

4.T

bit

-

-

TS_AFC

AFC Response Time

Receiver is ready

-

4.T

bit

-

-

TS_RSSI

RSSI Response Time

Receiver is ready

-

2.T

bit

-

-

DR_RSSI

RSSI Dynamic Range

AGC enabled

Min

Max

-

-

-115

0

-

-

dBm

dBm

* Set SensitivityBoost in RegTestLna to 0x2D to reduce the noise floor in the receiver

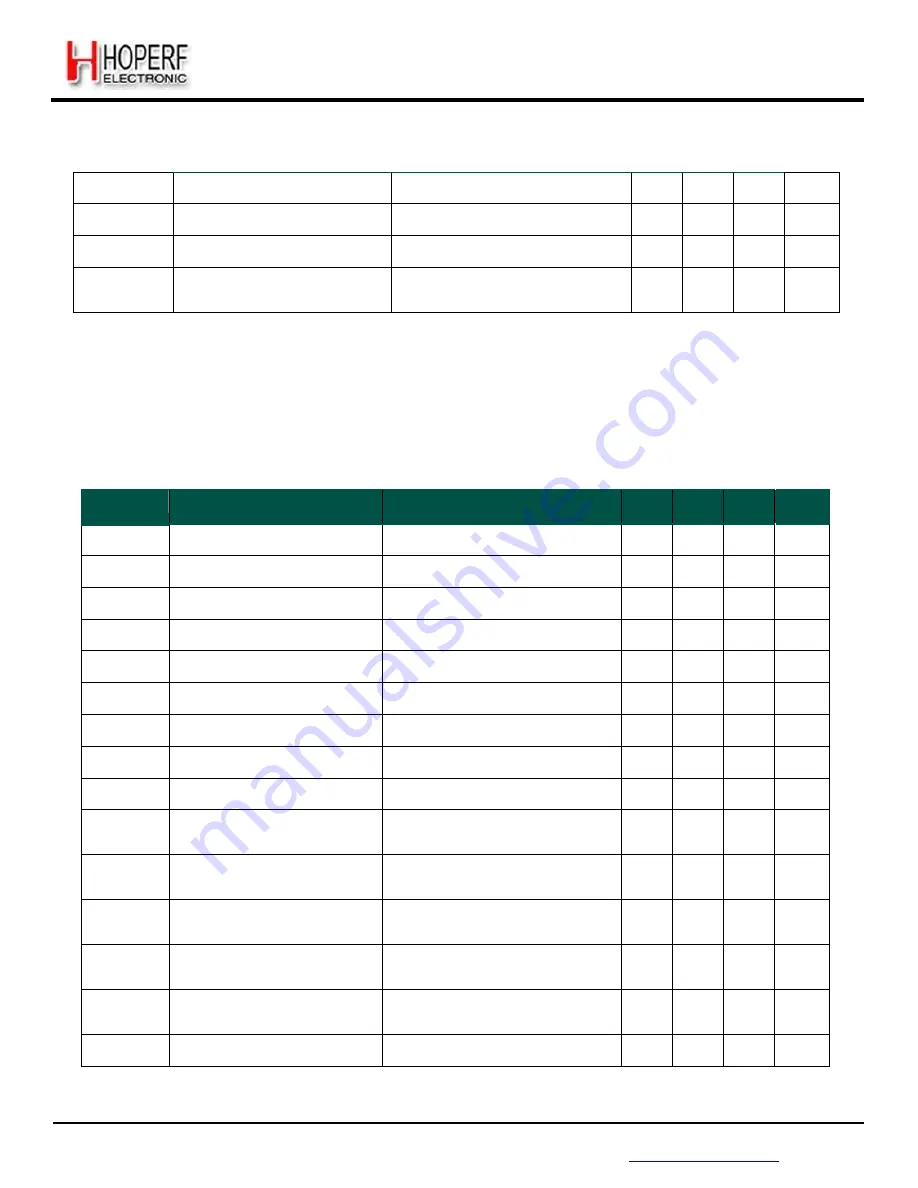

2.4.4. Digital Specification

Conditions: Temp = 25°C, VDD = 3.3V, FXOSC = 32 MHz, unless otherwise specified.

Table 7

Digital Specification

Symbol

Description

Conditions

Min

Typ

Max

Unit

V

IH

Digital input level high

0.8

-

-

VDD

V

IL

Digital input level low

-

-

0.2

VDD

V

OH

Digital output level high

Imax = 1 mA

0.9

-

-

VDD

V

OL

Digital output level low

Imax = -1 mA

-

-

0.1

VDD

F

SCK

SCK frequency

-

-

10

MHz

t

ch

SCK high time

50

-

-

ns

t

cl

SCK low time

50

-

-

ns

t

rise

SCK rise time

-

5

-

ns

t

fall

SCK fall time

-

5

-

ns

t

setup

MOSI setup time

from MOSI change to SCK rising

edge

30

-

-

ns

t

hold

MOSI hold time

from SCK rising edge to MOSI

change

60

-

-

ns

t

nsetup

NSS setup time

from NSS falling edge to SCK rising

edge

30

-

-

ns

t

nhold

NSS hold time

from SCK falling edge to NSS rising

edge, normal mode

30

-

-

ns

t

nhigh

NSS high time between SPI

accesses

20

-

-

ns

T_DATA

DATA hold and setup time

250

-

-

ns