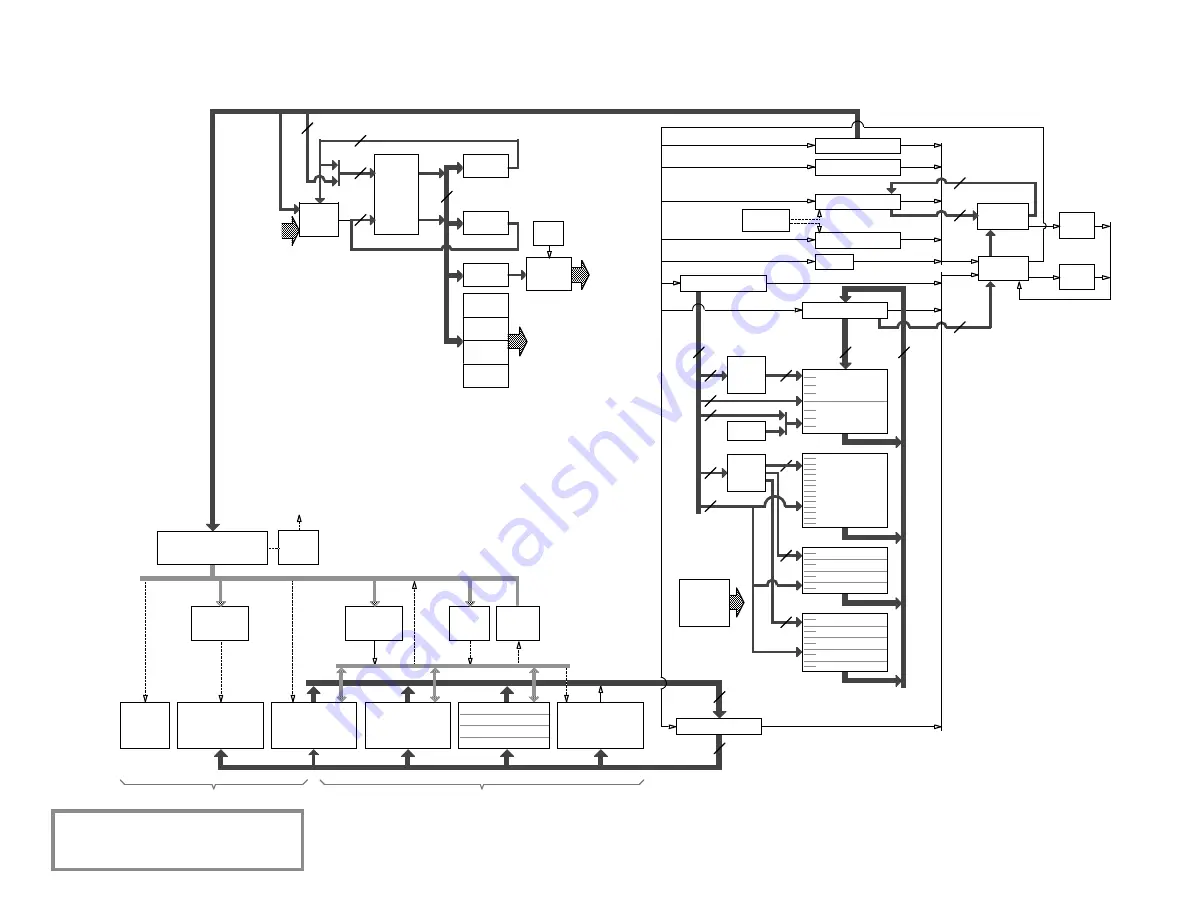

HP 9830 Computer

Section: Block Diagram

Page: N3

Rendition: 2014 Dec 26

Q Register - 16 bits

P Register - 16 bits

A Register - 16 bits

B Register - 16 bits

Binary ALU

(ROM 1)

E - 4 bits

BCD ALU

(ROM 2)

R-BUS

S-BUS

BCD

Carry FF

Binary

Carry FF

3

3

3

T-BUS

Processor Registers

Memory

Address

Memory

Write

Memory

Read

P Register = Program

Counter

Microcode

Address

Register

- 8 bits

Controls

8

4

4

Branch

Condition

Selector

Branch

Conditions

Microcode

ROM 5

Microcode

ROM 6

Microcode

ROM 7

Microcode

ROM 8

Microcode

ROM 9

Microcode

ROM 3

Microcode

ROM 4

Clock

Signals

8 MHz

Clock

Variable

Cycle

Generator

Microcode

Engine

SA

PA

SM

PM

PA / SA : Primary / Secondary Address

PM / SM : Address Modifier

Memory

Subsystem

RAM

Bank

Decoding

M Register -16 bits

RAM

2 * 4KW

BASIC ROM

7KW

BASIC II / 1KW

Cartridge ROMs

16

16

T Register -16 bits

Option ROMS

Memory

Cycle

State

Machine

Refresh

Counter

5

5

5

ROM

Bank

Decoding

6

9

15

3 * 1KW

5 * 1KW

8

14

8

10

I/O State Machine

& Command Decoding

I/O Subsystem

& Devices

DI / SI BUS

(Data / State In)

DO / SO / CO BUS

(Data / State / select-Code Out)

Alphanumeric LED

Display

Keyboard

@ Channel 16

& Select Code 12

Tape Drive

@ Select Code 10

9866 Printer

Interface

@ Select Code 15

Beeper

@ Channel 2

Display Enable

FF

@ Channel 8

Control Enable

FF

@ Channel 0/1

I/O Register - 16 bits

8+4

8+4+4

@ Various Select Codes

External I/O Slots

Service

Inhibit FF

Single

Service FF

CEO

CFI

SI0

SIH

SSI

CEO

Channel Devices

Select-Code Devices

QRD

FF

ALU

KLS

DEN

Interrupt

Control

A / B Select

FF

4

4