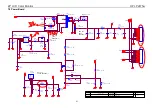

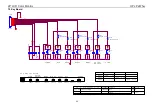

24" LCD Color Monitor HP LP2475w

27

R4

5

1

NC

G

Hurley 24W

Custom

7

10

Wednesday , June 04, 2008

<

称爹

>

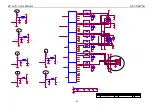

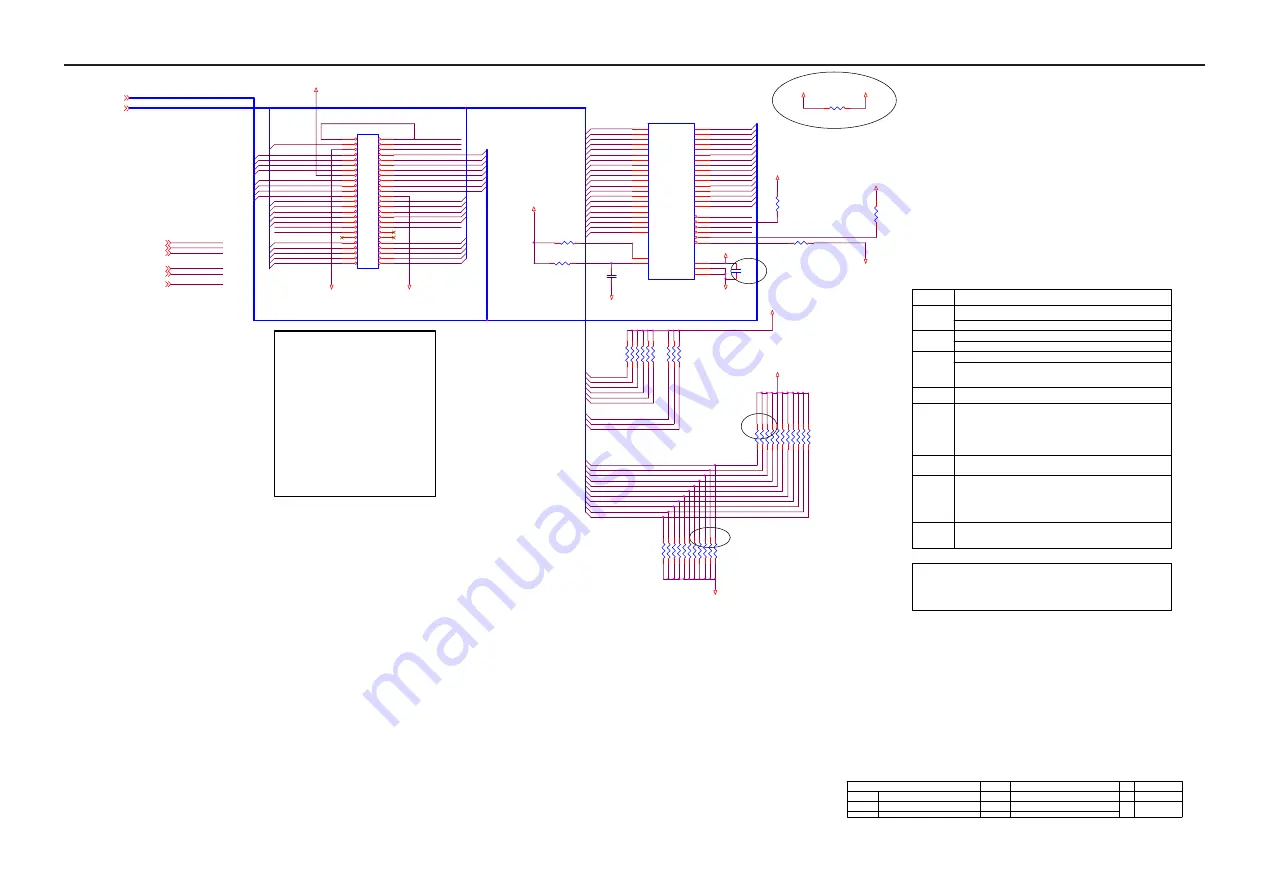

07. Memory I/F

T2972-G-X-X-1-080604

OEM MODEL

Size

Rev

Date

Sheet

of

TPV MODEL

PCB NAME

称爹

T P V ( Top Victory Electronics Co . , Ltd. )

Key Component

絬

隔

瓜

絪

腹

OCMADDR19

H

OCMDATA4

OCMADDR11

OCMADDR11

For Gene ral Purpose us e

L

R442

10K OHM 1/16W

/OCM_RE

R437 10K OHM 1/16W

L

OCMDATA8

BOOTSTRAP HEADER

OPEN=0

SHUNTED=1

Flash_Power

OCMDATA10

16:

OCMADDR10

OCMADDR17

/OCM_RE

OCMADDR7

18:

OCMDATA6

R4

5

6

10

K

O

H

M

1/

16

W

R4

5

8

10

K

O

H

M

1/

16

W

Flash_Power

GND

/OCM_WE

R4

6

1

10

K

O

H

M

1/

16

W

R4

4

5

10K

O

H

M

1/

16W

OCMADDR15

OCMADDR14

CN403

NC

1

2

3

4

5

6

7

8

9

10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

R4

6

5

10

K

O

H

M

1/

16

W

/BYTE

/OCM_CS1

OCMADDR6

OCMADDR1

15:

OCMDATA0

/OCM_RE

OCMADDR[0..21]

R443

10K OHM 1/16W

R439

10K OHM 1/16W

Open (Internal ROM on, and m apped to top 32K)

Clos e (Internal ROM off-boot from ext ROM )

OCMADDR17

OCMDATA[0..15]

OCMADDR9

00 = I2C to JTAG Bridge disabled

01 = ICD_SDA on VGA0_SDA, ICD_SCL on VGA0-SCL

10 = ICD_SDA on VGA1_SDA, ICD_SCL on VGA1_SCL

11 = I2C to JTAG bridge disabled, 5 JTAG signals m apped

to AVS Pins

+3.3V_I/O

OCMDATA5

OCMADDR4

1 = Stay in IntRom without checking any DDC2Bi channel. (ForceDebug)

OCMDATA0

3/21 Change

120 BEAD

OCMADDR[0..21]

0 = After power on Reset, continue the boot up using internal ROM

7

/ROM_CS

/RESET

OCMDATA1

OCMADDR13

OCMADDR7

R4

5

7

10

K

O

H

M

1/

16

W

H

OCMDATA13

OCMADDR8

GND

GND

R4

6

3

NC

OCMADDR7

OCMDATA2

OCMDATA10

H

/OCM_WE

/OCM_CS1

OCMADDR19

R4

5

5

10

K

O

H

M

1/

16

W

FB401

0 OHM 1/8W

6:0:

OCMDATA3

OCMADDR5

R4

5

9

NC

/OCM_CS0

OCMDATA9

OCMADDR16

OCMADDR19

L

OCMDATA12

OCMDATA5

JP 804 do not care

+3.3V_I/O

OCMDATA14

R441

10K OHM 1/16W

Samtec FTR-125-01-S-D

9

OCMDATA1

OCMADDR1

OCMADDR5

OCMADDR17

OCMDATA4

OCMADDR18

14:

Jumper Note:

OCMADDR20

1 = Use DDCB2Bi Channel #1

OCMDATA6

OCMDATA14

/OCM_WE

/RESET

Foot Print for a X16 Flas h

OCMADDR3

OCMADDR15

1 = Perform power up code CRC check. If the CRC check did not match

the one stored in the XROM Configure block, blink a led at a rate of 2

second per blink

OCMDATA3

OCMADDR2

OCMADDR14

OCMADDR0

OCMDATA7

OCMADDR3

OCMADDR13

OCMADDR8

3/21 CLOSE TO

PIN37

+3.3V_I/O

+3.3V_I/O

OCMDATA2

/OCM_RE

/ROM_CS

/ROM_CS

OCMDATA11

OCMADDR12

OCMADDR3

OCMADDR2

R4

5

0

10K

O

H

M

1/

16W

0 = Do not perform power up code CRC check

OCMADDR18

OCMADDR14

R4

5

4

NC

Open/0 (Exte rnal Oscillator on TCLK pin)

Clos e/1 (XTAL and Internal Oscillator)

R4

6

0

NC

/OCM_CS

R4

4

6

10K

O

H

M

1/

16W

OCMADDR21

H

OCMDATA12

OCMADDR15

OCMADDR9

GND

OCMDATA8

R4

4

9

10K

O

H

M

1/

16W

R440

10K OHM 1/16W

OCMADDR11

OCMADDR10

/OCM_CS1

OCMDATA9

R430

10K OHM 1/16W

OCMADDR[0..21]

OCMADDR6

OCMADDR12

OCMADDR16

OCMDATA7

19:

R4

4

7

10K

O

H

M

1/

16W

000 = 20-bit address , 8-bit EXT I/F

001 = 24-bit address , 8-bit EXT I/F

010 = 20-bit address , 16-bit EXT I/F

011 = 24-bit address , 16-bit EXT I/F

1XX = OCM disable d, external

parallel control bus (tes tbench)

PROM JET Em ulator Header for a X16 m em ory

OCMDATA13

/OCM_WE

GND

OCMADDR13

R4

4

8

NC

JP 806,JP807 and JP808 HI-LO setting:

L

OCMADDR6

R433

10K OHM 1/16W

8

OCMADDR21

R4

4

4

NC

Flash_Power

OCMDATA[0..15]

OCMADDR10

R4

6

4

NC

JP 801, JP805, JP802, JP803

are linking 1&2.

OCMADDR0

OCMADDR9

OCMADDR20

+3.3V_I/O

OCMADDR2

13:

NC On Prom jet

OCMDATA15

H

R434

10K OHM 1/16W

OCMADDR4

R438 10K OHM 1/16W

/OCM_CS0

R436 10K OHM 1/16W

L

GND

OCMADDR5

OCMADDR12

OCMADDR8

R432

10K OHM 1/16W

U408

MX29LV320CTTC-90G

1

2

3

4

5

6

7

8

18

19

20

21

22

23

24

25

45

43

41

39

36

34

32

30

26

28

11

37

27

17

48

44

42

40

38

35

33

31

29

47

12

15

9

10

13

14

16

46

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

DQ15/A1

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

CE#

OE#

WE#

VCC

VSS

A17

A16

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

BYTE#

RESET#

Ready /Busy #

A19

A20

NC

/WP_ACC

A18

VSS

+3.3V_I/O

C536

1uF/16V

/OCM_CS0

C424

0.1UF16V

I2C to JTAG bridge address or Gene ral use

17:

L

R445/10K/0402,R464/NC

0 = Use DDCB2Bi Channel #0

/RESET

OCMADDR18

R435 10K OHM 1/16W

R4

5

2

NC

OCMDATA11

OCMADDR4

OCMADDR16

R431

10K OHM 1/16W

Please define the default

value, NC or populate

10K

R4

5

3

NC

OCMDATA15

OCMADDR1

R4

6

2

NC

10-12

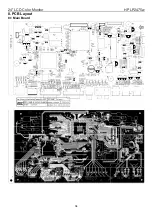

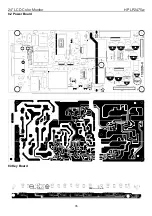

Summary of Contents for LP2475w - 24" LCD Monitor

Page 3: ...24 LCD Color Monitor HP LP2475w 3 1 Monitor Specification ...

Page 7: ...24 LCD Color Monitor HP LP2475w 7 ...

Page 8: ...24 LCD Color Monitor HP LP2475w 8 ...

Page 9: ...24 LCD Color Monitor HP LP2475w 9 ...

Page 10: ...24 LCD Color Monitor HP LP2475w 10 ...

Page 14: ...24 LCD Color Monitor HP LP2475w 14 4 2 Factory Preset Display Modes ...

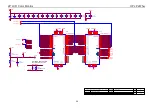

Page 34: ...24 LCD Color Monitor HP LP2475w 34 8 PCB Layout 8 1 Main Board ...

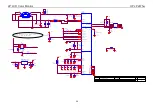

Page 35: ...24 LCD Color Monitor HP LP2475w 35 8 2 Power Board 8 3Key Board ...

Page 36: ...24 LCD Color Monitor HP LP2475w 36 8 4 USB Board ...

Page 50: ...24 LCD Color Monitor HP LP2475w 50 The panel The end ...