ESMT

M12L64164A

Elite Semiconductor Memory Technology Inc.

Publication Date: May 2008

Revision: 3.3

41/46

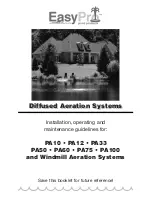

Active/Precharge Power Down Mode @ CAS Latency = 2, Burst Length = 4

C L O C K

C K E

C S

R A S

C A S

A D D R

W E

D Q

D Q M

A 1 0 / A P

B A 1

A c t i v e

P o w e r - d o w n

E x i t

P r e c h a r g e

: D o n ' t c a r e

* N o t e 3

* N o t e 2

* N o t e 1

t

S S

t

S S

t

S S

Q a 0

Q a 1

Q a 2

t

S H Z

P r e c h a r g e

P o w e r - D o w n

E n t r y

P r e c h a r g e

P o w e r - D o w n

E x i t

R o w A c t i v e

A c t i v e

P o w e r - d o w n

E n t r y

R e a d

0

1

2

3

4

5

6

7

8

9

1 0

11

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

B A 0

R a

R a

C a

*Note: 1. Both banks should be in idle state prior to entering precharge power down mode.

2. CKE should be set high at least 1CLK + t

SS

prior to Row active command.

3. Can not violate minimum refresh specification. (64ms)