Operator Guide

A-8

BPP External LoopBack Test (BPP EXT L–B TEST

)

Note: This test can only be performed by Field or Manufacturing people.

This test checks the accessibility of the Super–IO chip. It saves and restores used registers.

This test is not performed at power on.

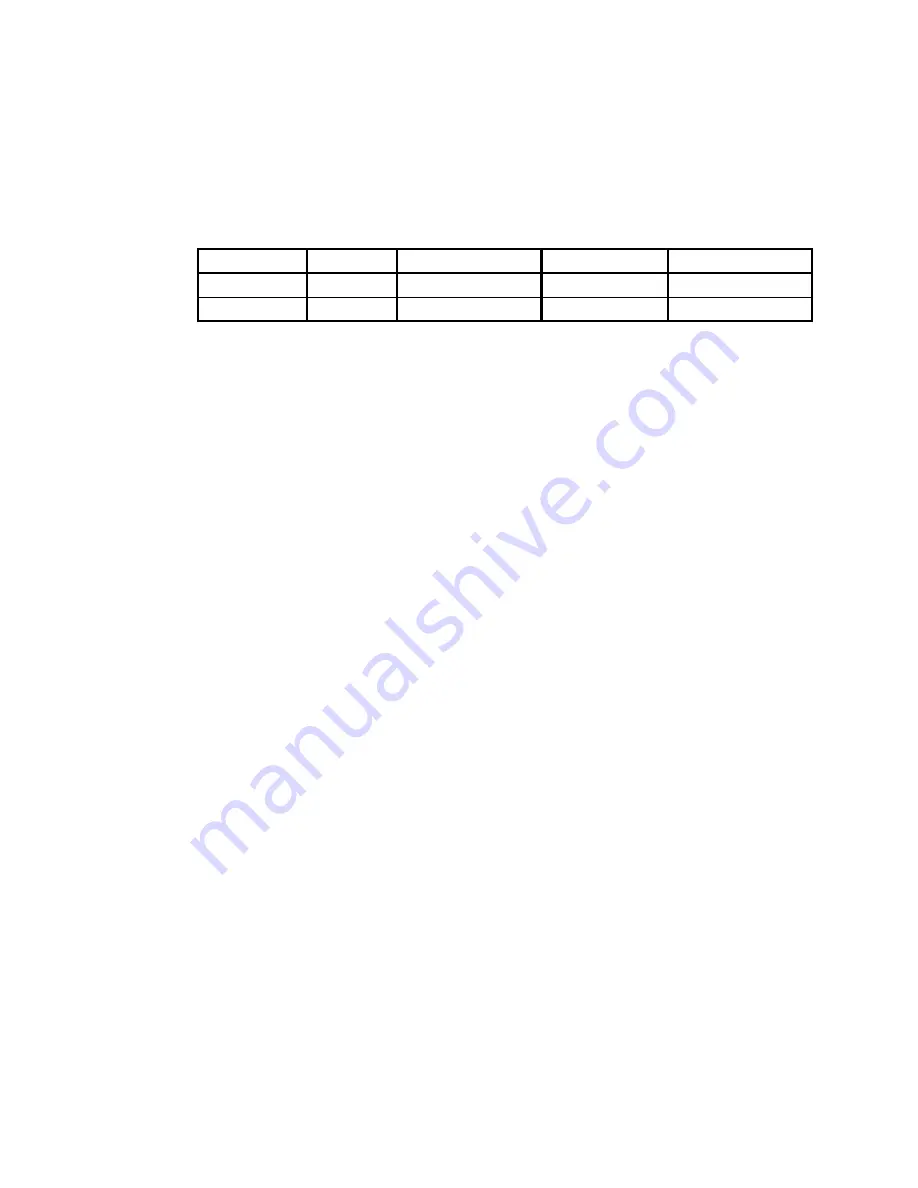

Entry Parameters

Parameters

Name

Definition

Possible Values Default Value

Parameter 1

Sub test #

Subtest Number

0 or 1

0 = All tests linked

Parameter 2

Proc #

Processor Number

8

8 = BUMP

JTAG Test Group

These tests check the chip to chip connections using the JTAG features. These tests are run

automatically by the BUMP.

The following three tests are available under this group:

Nodes Detection Test

This test detects all the connections between the chips. These detected nodes can be

stored on a Floppy diskette and loaded to NVRAM under the Maintenance menu, as soon as

a JTAG test is to be performed.

This test uses the JTAG capabilities to read or set the pins of the chips. This test builds a

node which is made up of set of pins which are linked, or pins which are not linked to a

node but directly linked to Vcc or GND (pull-up or pull-down). The nodes are stored in the

“nodes” file.

Fast Test

This test processes all the nodes of the “nodes” file, in order to check the integrity of the

links between the chips. This test checks if an error is present but doesn’t localize the errors.

When an error is detected, the test stops and the error is reported.

Diagnosis Test

This test checks all the nodes of the “nodes” file, looking for any differences between what is

read via JTAG and what has been memorized in the “nodes” file. If an error is detected, it is

stored in the “faults” file. This test is slow but it localizes the problems.

When JTAG tests are selected under the Off Line Test Control, the JTAG Test Monitor menu

is displayed. This menu performs the following main functions,

•

Test Execution: Execution of the preceding tests in Normal or Trace mode (step by step).

•

Display Nodes files / Faults Files: It is possible to view the entire nodes file / faults file.

•

Display Configuration File: To view the hardware specific information (like the input pins,

Tri-stated pins, number of boards, etc).

More information about JTAG tests is awaited.

Direct I/O Test Group

These tests are performed by all processors at Power-On and are under control of the Off

Line Test monitor. These tests check the accessibility of the Standard and Direct I/O

components from the CPUs. The following tests are available under this group.

Summary of Contents for 7015-R30

Page 1: ...7015 Models R30 R40 and R50 CPU Enclosure Installation and Service Guide...

Page 10: ...x Service Guide...

Page 14: ...xiv Service Guide...

Page 34: ...1 20 Service Guide...

Page 214: ...6 10 Service Guide Detail 5 CPU Module 2 of 3 26 27 29 30 31 32 33 34 28 35...

Page 216: ...6 12 Service Guide Detail 6 CPU Module 3 of 3 36 37...

Page 252: ...B 8 Installation and Service Guide...

Page 288: ...Service Guide D 30...

Page 299: ......