SystemGuard Test Groups

A-17

ECC Data Lines Accessibility Test

This test checks the accessibility for all the data lines to the ECC memory banks, through

SMC ASICs. The following hardware parts are checked by running this test.

•

DCB ASICs

•

SMC ASICs

•

Connection of data lines between CPU daughter boards and MPB ASICs

•

Connection of data lines between MPB ASICs and ECC memory chips.

Words manipulated / used are not restored at the end of the test. This test is applied to all

present memory banks.

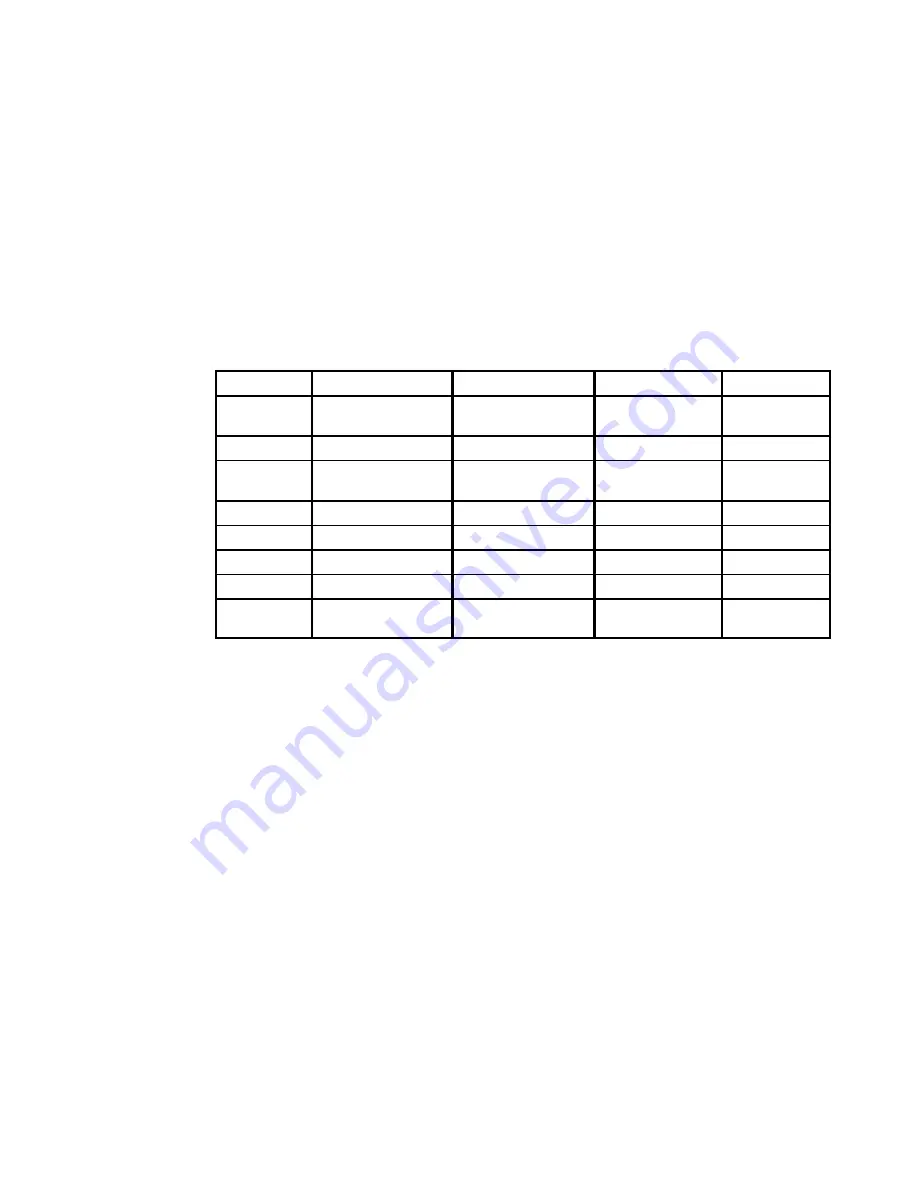

Entry Parameters

Parameters

Name

Definition

Possible Values

Default Value

Parameter 1 Sub test #

Subtest Number

0 to 2

0 = All tests

linked

Parameter 2 Proc #

Processor Number

0 to 7

0

Parameter 3 ECC sel.

ECC Selection

0 to 5

See note 1

2

Parameter 4 1

st

Mem. Bnk Add.

Mem Address (Mb)

0

Parameter 5 2

nd

Mem. Bnk Add. Mem Address (Mb)

0xffffffff

Parameter 6 3

rd

Mem. Bnk Add.

Mem Address (Mb)

0xffffffff

Parameter 7 4

th

Mem. Bnk Add.

Mem Address (Mb)

0xffffffff

Parameter 8 SIMM/Bus mode

See note 2

0=SIMM number

1=Value of Bus

0

Notes:

1. The different values are:

. 0 –> ECC invalidation,

. 1 –> ECC validation and checkstop detection,

. 2 –> ECC test,

. 3 –> ECC validation and no checkstop detection,

. 4 –> ECC generation checking,

. 5 –> ECC correction checking.

2. If your answer is 0, you get the number of the default DIMM.

If your answer is 1, you get the bus value which enables you to determine the

failing bits.

Work Area Checking

This program calculates the memory address available on each board to perform the sub

tests. If no working area exists, a fatal error message is displayed on the console.

Walking 1 Data Test

This test basically identifies if any ECC data lines are stuck at level 0 or to any other ECC

data line. This test writes a pattern of a single1 bit among 0 bits on the cache line. Then it is

read and compared.

Walking 0 Data Test

This test isolates an open line among the ECC data lines. It writes a pattern of a single 0 bit

among 1 bits on the cache line. Then it is read and compared.

Summary of Contents for 7015-R30

Page 1: ...7015 Models R30 R40 and R50 CPU Enclosure Installation and Service Guide...

Page 10: ...x Service Guide...

Page 14: ...xiv Service Guide...

Page 34: ...1 20 Service Guide...

Page 214: ...6 10 Service Guide Detail 5 CPU Module 2 of 3 26 27 29 30 31 32 33 34 28 35...

Page 216: ...6 12 Service Guide Detail 6 CPU Module 3 of 3 36 37...

Page 252: ...B 8 Installation and Service Guide...

Page 288: ...Service Guide D 30...

Page 299: ......