EM78M611E

Universal Serial Bus Series Microcontroller

Product Specification

(V1.11) 04.20.2007

••••

11

(This specification is subject to change without further notice)

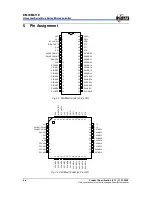

A12 A11 A10

A9 A8

A7~A0

0000

Page 0

03FF

0400

Page 1

07FF

0800

Page 2

0BFF

1000

Page 0

13FF

1400

Page 0

17FF

Stack 1

Stack 2

Stack 3

Stack 4

Stack 5

Stack 6

Stack 7

Stack 8

Call

Interrupt

RET

RETL

RETI

0000 : Reset Vector

0001 : Interrupt Vector

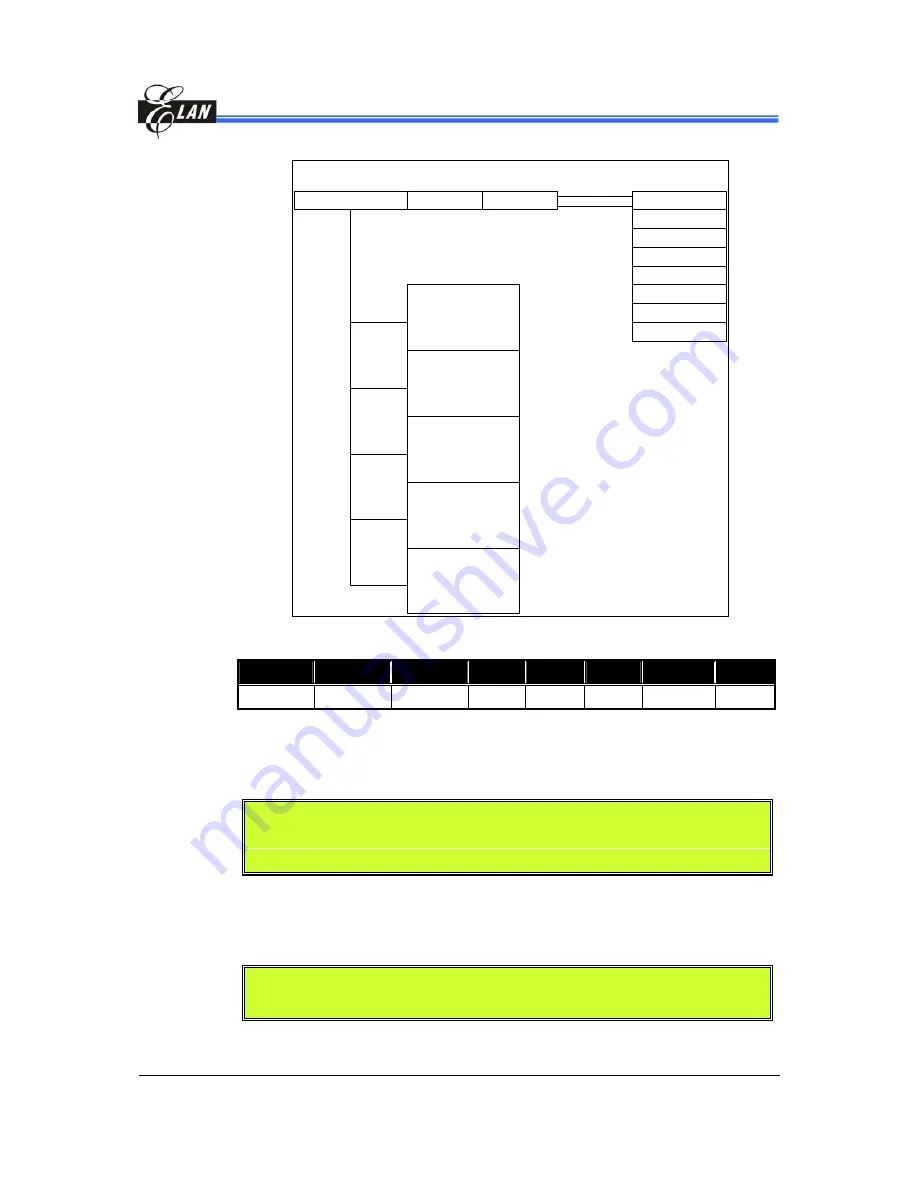

8.2.2.4 R3 (Status Register)

Default Value:(0B_0001_1XXX)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

PS2

PS1

PS0

T

P

Z

DC

C

R3 [0] Carry/Borrow Flag

0

= No carry-out from the result’s Most Significant bit

1

= A carry-out from the result’s Most Significant bit occurred

NOTE

For Borrow, the polarity is reversed. For rotate (RRC, RLC) instructions, this bit is

loaded with either high or low-order bit of the source register.

R3 [1] Auxiliary Carry/Borrow Flag

. For ADD, SUB Instructions

0

= No carry-out from the 4th low-order bit of the result

1

= A carry-out from the 4th low-order bit of the result occurred

NOTE

For Borrow, the polarity is reversed.