EM78P312N

8-Bit Microcontroller

12

•

Product Specification (V1.0) 10.03.2006

(This specification is subject to change without further notice)

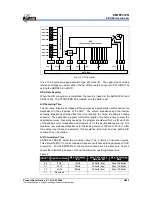

Bank 1 R8 TC2CR/ ADDL (Timer/Counter 2 Control Register, AD Low 2 bits

Data Buffer)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

ADD1 ADD0

0

TC2M TC2S TC2CK2

TC2CK1

TC2CK0

Bit 7 ~ Bit 6 ( ADD1 ~ ADD0 )

:

AD low 2-bit data buffer

Bit 4 ( TC2M ) :

Timer/Counter 2 mode select

TC2M = “0” :

Timer/counter mode

TC2M = “1” :

Window mode

Bit 3 ( TC2S )

:

Timer/Counter 2 start control

TC2S = “0” :

Stop and counter clear

TC2S = “1” :

Start

Bit 2 ~ Bit 0 ( TC2CK2 ~ TC2CK0 ) :

Timer/Counter 2 Clock Source Select

TC2CK2

TC2CK1

TC2CK0

Clock Source

( Normal, Idle )

Resolution

( Fc=8M )

Max. Time

( Fc=8M )

0 0 0

Fc/

2

23

1.05s

19.1h

0 0 1

Fc/

2

13

1.02ms

1.1min

0 1 0

Fc/

2

8

32

μ

s 2.1s

0 1 1

Fc/

2

3

1

μ

s 65.5ms

1 0 0

Fc

125ns 7.9ms

1 0 1

-

-

-

1 1 0

-

-

-

1

1

1

External clock (TC2 pin)

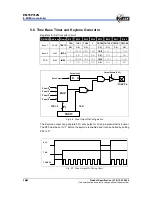

Bank 1 R9 TC2DH (Timer 2 Data Buffer High Byte)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC2D15 TC2D14 TC2D13 TC2D12 TC2D11 TC2D10 TC2D9 TC2D8

Bit 7 ~ Bit 0 ( TC2D15 ~ TC2D8 ) :

16-bit Timer/Counter 2 data buffer high byte.

Bank 1 RA TC2DL (Timer 2 Data Buffer Low Byte)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC2D7 TC2D6 TC2D5 TC2D4 TC2D3 TC2D2 TC2D1 TC2D0

Bit 7 ~ Bit 0 ( TC2D7 ~ TC2D0 ) :

16-bit Timer/Counter 2 data buffer low byte.

Bank 1 RB ADCR (AD Control Register)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

ADREF ADRUN ADCK1 ADCK0 ADP ADIS2 ADIS1 ADIS0

Bit 7 ( ADREF ) :

AD reference voltage input select.

ADREF = “0” :

Internal VDD, P97 is used as IO.

ADREF = “1” :

External reference pin, P97 is used as reference input pin.