prel

imin

ary

prel

imin

ary

iC-TW29

26-BIT ENCODER PROCESSOR

WITH INTERPOLATION AND BiSS INTERFACE

Rev C1, Page 13/28

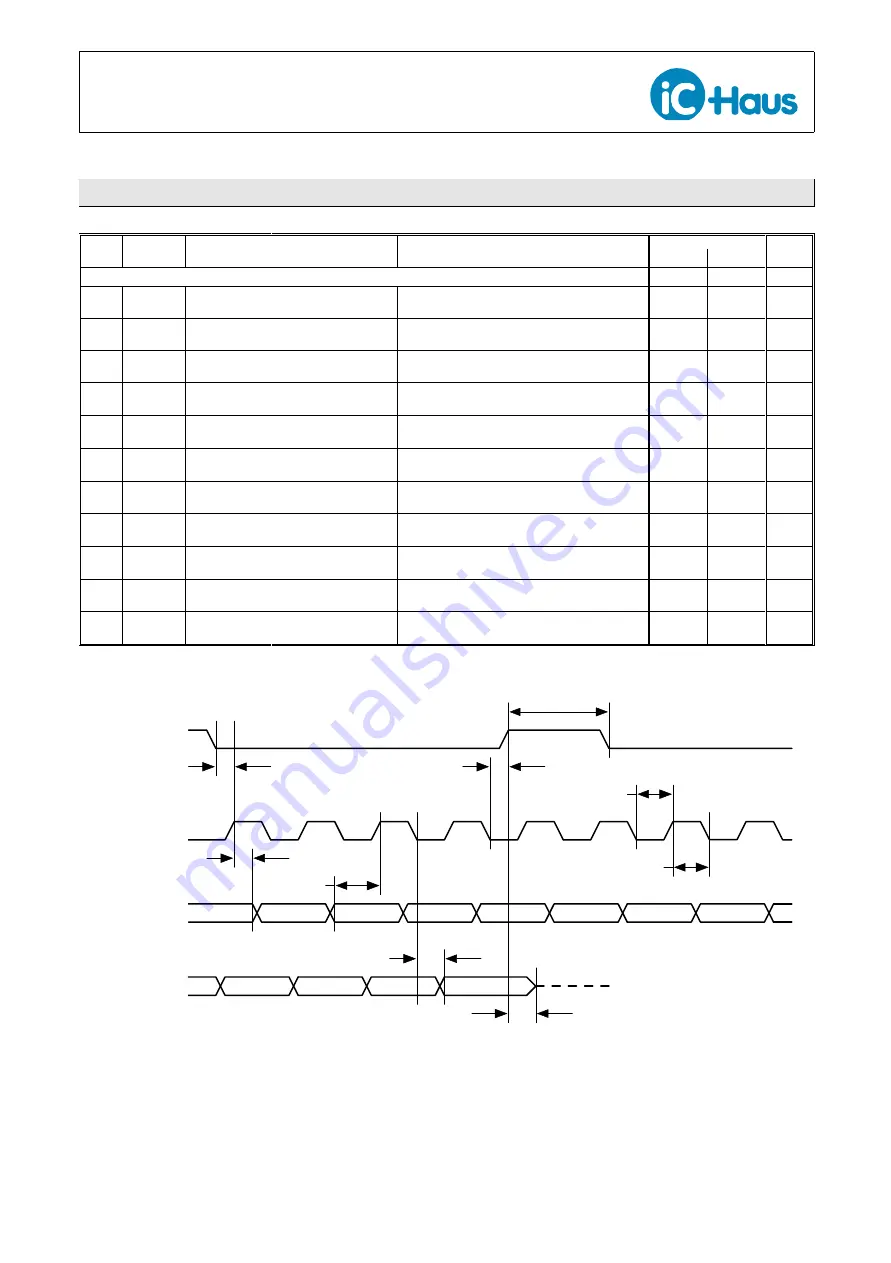

OPERATING REQUIREMENTS: SPI Interface

Operating conditions: AVDD = DVDD = IOVDD = +3.1...+3.6 V, AVSS = DVSS = IOVSS = 0 V, Tj = –40...125

°

C

Item

Symbol

Parameter

Conditions

Unit

No.

Min.

Max.

SPI Interface Timing

I001 t

C1

Permissible Clock Cycle Time

(See spec. item 704)

TEST.spi = 0

50

ns

TEST.spi = 1

25

ns

I002 t

D1

Clock Signal Lo Level Duration

TEST.spi = 0

15

ns

TEST.spi = 1

7.5

ns

I003 t

D2

Clock Signal Hi Level Duration

TEST.spi = 0

15

ns

TEST.spi = 1

7.5

ns

I004 t

S1

Setup Time:

xSS lo before SCLK lo

→

hi

80

ns

I005 t

H1

Hold Time:

xSS lo after SCLK hi

→

lo

50

ns

I006 t

W1

Wait Time: between

xSS lo

→

hi and xSS hi

→

lo

200

ns

I007 t

S2

Setup Time:

SI stable before SCLK lo

→

hi

5

ns

I008 t

H2

Hold Time:

SI stable after SCLK lo

→

hi

10

ns

I009 t

P1

Propagation Delay:

SO stable after xSS hi

→

lo

60

ns

I010 t

P2

Propagation Delay:

SO high impedance after xSS lo

→

hi

25

ns

I011 t

P3

Propagation Delay:

SO stable after SCLK hi

→

lo

20

ns

xSS

SCLK

SI

SO

tW1

tD1

tD2

tS1

TSI(hold)

TSI(set)

TSO(prop)

tH1

TSO(float)

Hi-Z

Figure 6: SPI Timing