4 - 6

Shift register

Prescaler

Phase

detector

Loop

filter

Programable

counter

Programable

divider

X2

29.6 MHz

“2nd LO” signal

to the FM IF IC

14

Q59, D39, D45–D47

RX VCO

TX VCO

Buffer

Buffer

Buffer

Q28

Q29

Q60

3

8

4

5

PLST

IC3 (TB31207)

SO

SCK

to transmitter circuit

to 1st mixer circuit

D17

D6

9

Q58, D38, D48

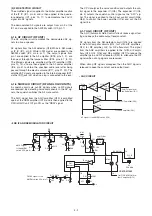

4-4 POWER SUPPLY CIRCUITS

VOLTAGE LINES (MAIN UNIT)

LINE

DESCRIPTION

HV

The voltage from the connected DC power

supply.

VCC

The same voltage as the HV line or battery

voltage through the power switch (Q24, D19,

D22).

CPU 5

Common 5 V converted from the HV line at

the CPU5V regulator circuit (LOGIC unit;

IC3). The output voltage is applied to the

CPU (LOGIC unit; IC1), reset IC (LOGIC

unit; IC2) and EEPROM (LOGIC unit; IC7),

etc.

+5V

Common 5 V converted from the VCC line

by the +5 V regulator circuit (LOGIC unit;

IC16, Q4, Q6, Q7, D10). The output voltage

is applied to the PLL IC (RF unit; IC3) and

D/A convertor IC (RF unit; IC17), etc.

T5V

Transmit 5 V controlled by the T5V regula-

tor circuit (RF unit; Q7, Q8, D8) using TXC

signal from the CPU (LOGIC unit; IC1). The

output voltage is applied to the buffer ampli-

fier (RF unit; Q6) and pre-driver (RF unit;

Q4), etc.

R5S

Receive 5 V controlled by the R5S regulator

circuit (Q20) using R5C signal from the CPU

(LOGIC unit; IC1). The output voltage is ap-

plied to the RF amplifi er (RF unit; Q12) and

1st IF amplifi er (RF unit; Q13), etc.

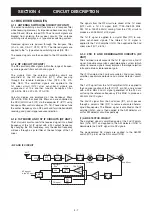

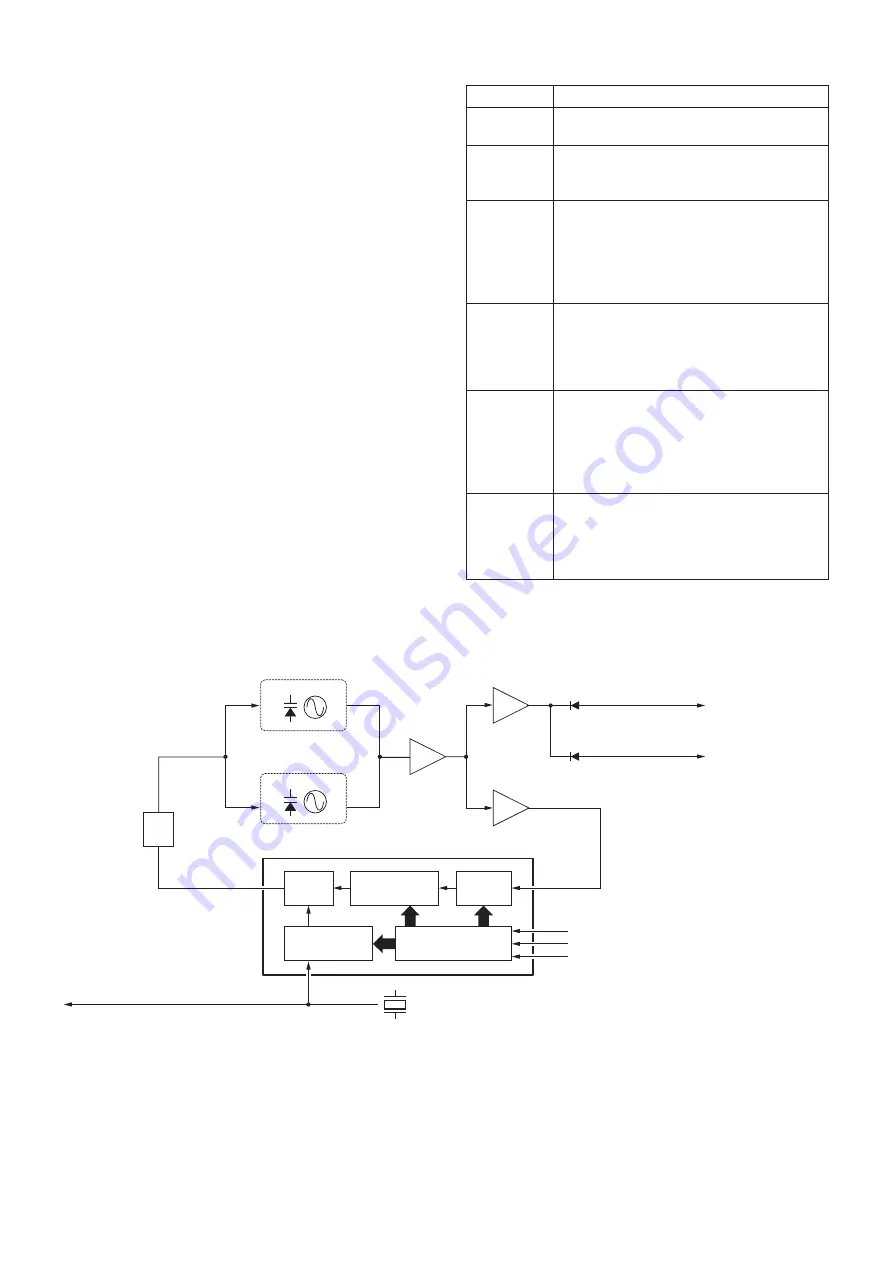

4-3 PLL CIRCUITS (RF UNIT)

A PLL circuit provides stable oscillation of the transmit

frequency and receive 1st LO frequency. The PLL output

compares the phase of the divided VCO frequency to the

reference frequency. The PLL output frequency is controlled

by the divided ratio (N-data) of a programmable divider.

The PLL circuit contains the TX VCO circuit (Q58, D38,

D48) and RX VCO circuit (Q59, D39, D45–D47). The oscil-

lated signal is amplified at the buffer-amplifiers (Q60, Q29)

and then applied to the PLL IC (IC3, pin 8).

The PLL IC contains a prescaler, programmable counter,

programmable divider and phase detector, etc. The entered

signal is divided at the prescaler and programmable counter

section by the N-data ratio from the CPU. The divided signal

is detected on phase at the phase detector using the refer-

ence frequency.

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the oscillated frequency.

A portion of the VCO signal is amplified at the buffer-ampli-

fier (Q28) and is then applied to the receive 1st mixer (Q12)

or transmit buffer-amplifier circuit (Q6) via the T/R switches

(D6, D17).

• PLL CIRCUIT