4.8.5 The MagicScan Function

The features of MagicScan are given as follows:

1.

Different gain for each channel

2.

Non-sequential order for channel scan

3.

Different sampling rate for each channel (use with digital filter)

4.

Programmable different digital filter for each scan channel

5.

Programmable HI/LO alarm for each channel

6.

Three external trigger: post-trigger, pre-trigger and middle-trigger

7.

Maintain at 330 k max. for total channel scan

8.

Easy programming

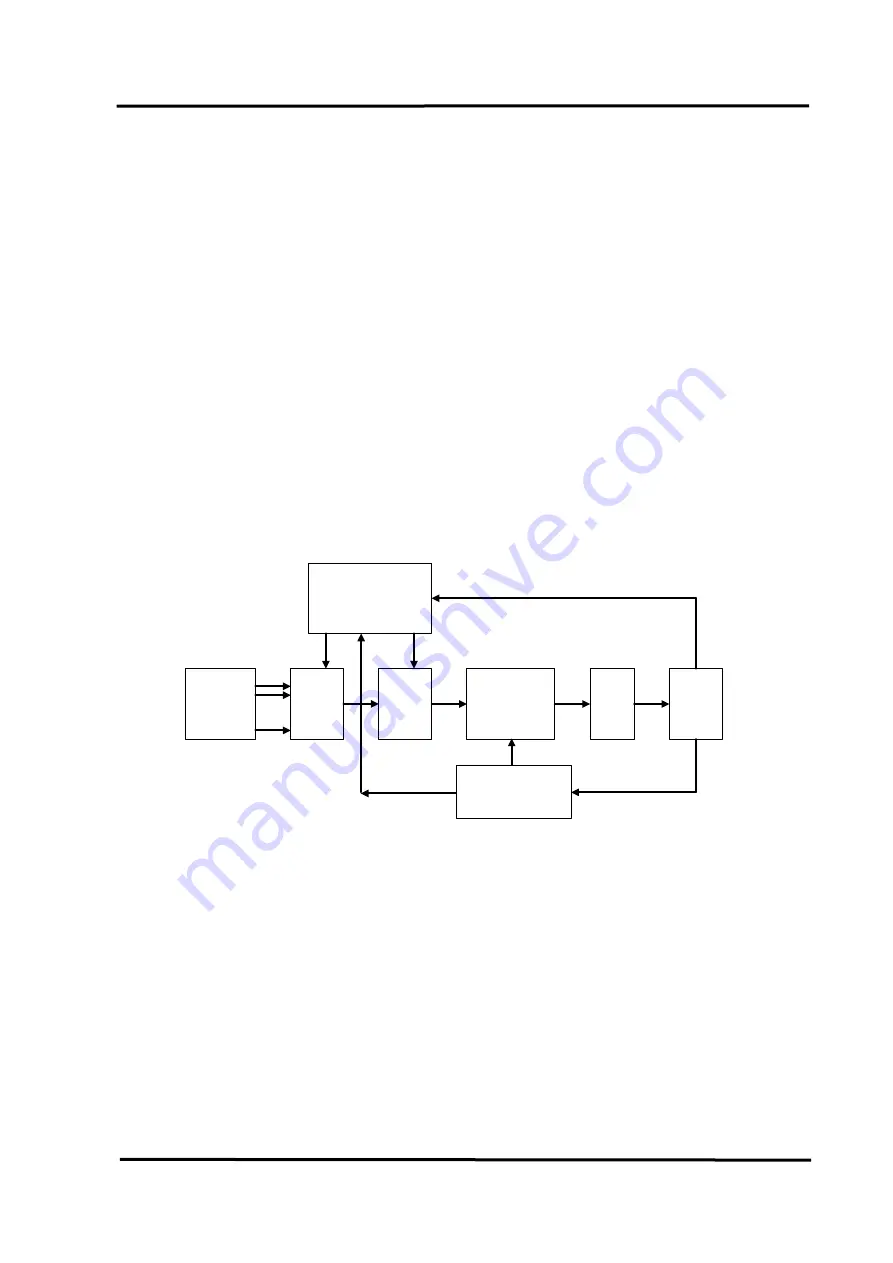

The MagicScan function is implemented with software and hardware. The feature 1 and

feature 2 are implemented in hardware. The other features are implemented in software. The

block diagram of MagicScan function is given as follows:

Analog

Signal

MUX

PGA

A/D

Converter

FIFO

X86

Pacer Trigger

Timer

Magic Scan

Controller

:

:

(1) The Magic Scan controller is a high performance RISC-like controller. It can scan the

analog input signal in non-sequential order. It also control the PGA to different

predefined gain for each channel.

(2) The pacer trigger timer will be generated the trigger signal to A/D converter.

(3) The A/D conversion data will enter the FIFO.

(4) The X86 will read and analyze the A/D data from FIFO while the CPU is ready. The

FIFO is 1 k samples for PCI-1800 and 8 k samples for PCI-1802. The X86 will compute and

analyze the A/D data while the A/D conversion is going. Therefore the speed of X86 must

compatible with the speed of A/D conversion. The A/D conversion can be 330 k max. in the

channel/scan mode. Therefore the X86 must handle 330 k samples per second to avoid

overflow. The Pentium-120 CPU or more powerful CPU is recommended.

PCI-1202/1602/1800/1802 Hardware User’s Manual

(

Ver.4.2, Dec/2009, PMH-014-42)---- 76