14. Register Descriptions > PCIe Capability Registers

181

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

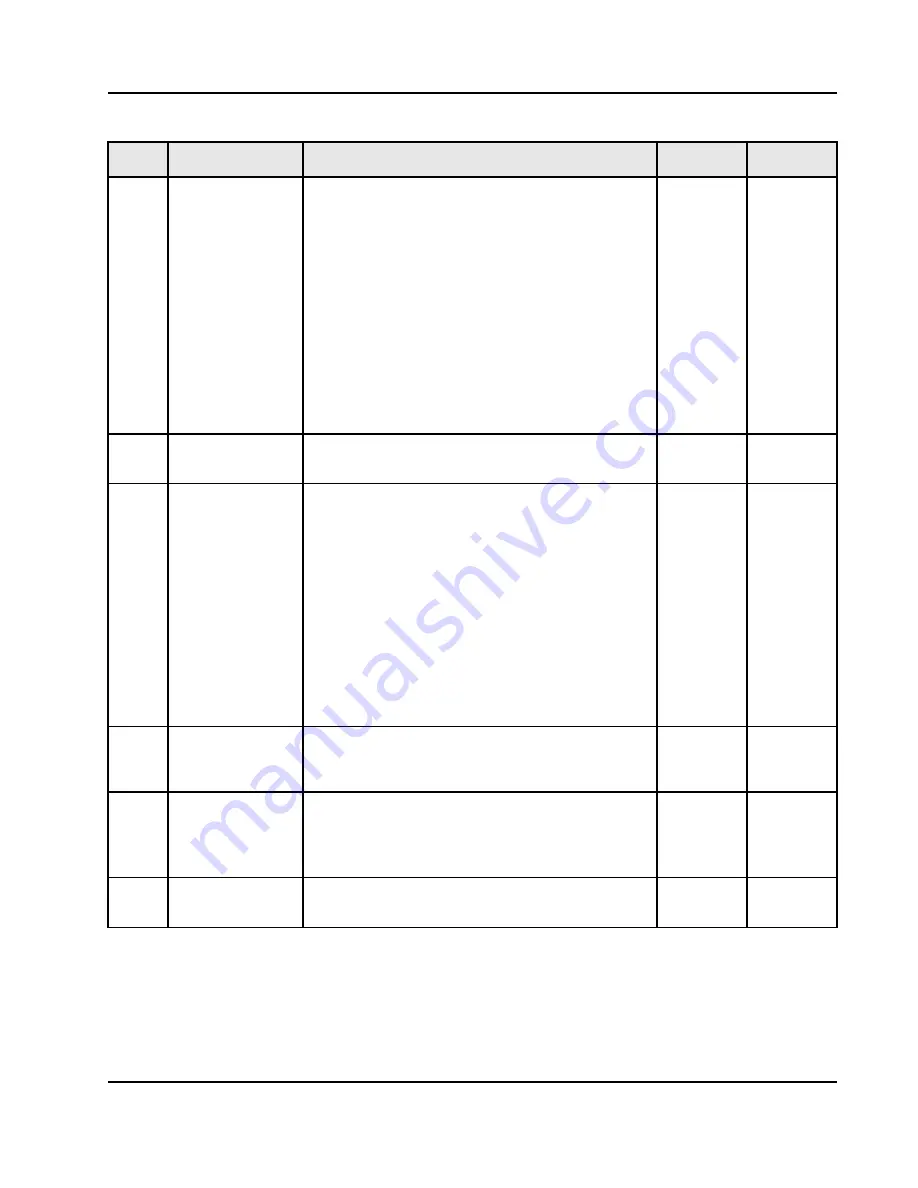

18

CLK_PWR_MGT

Clock Power Management

0 = The component does not have this capability, and the

reference clock(s) must not be removed in these link states.

1 = The component tolerates the removal of any reference

clock(s) via the “clock request” (CLKREQ#) mechanism

when the link is in the L1 and L2/3 Ready link states.

This capability is applicable only in form factors that support

“clock request” (CLKREQ#) capability.

For a multifunction device, each function indicates its

capability independently. Power Management configuration

software must only permit reference clock removal if all

functions of the multifunction device indicates a 1 in this bit.

Note: The PEB383 does not support CLK_PWR_MGT. This

field always reads 0.

R

0

17:15

L1_EXIT

PCIe L1 Exit Latency

L1 exit latency is between 2 and 4 us.

RWL

010

14:12

L0S_EXIT

PCIe L0s Exit Latency

The PEB383 L0s exit latency will be as 256-512ns which will

be reported as 0b011. This value can be overwritten by the

serial EEPROM.

000 = Less than 64 ns

001 = 64 ns to less than 128 ns

010 = 128 ns to less than 256 ns

011 = 256 ns to less than 512 ns

100 = 512 ns to less than 1 us

101= 1 us to less than 2us

110 = 2-4 us

111 = More than 4 us

RWL

011

11:10

ASPM

PCIe ASPM Support

The PEB383 supports the L0s and L1 ASPM state. This field

always returns 11.

R

11

09:04

MAX_WIDTH

PCIe Maximum Link Width

This field indicates the maximum number of PCIe lanes that

can be used for communicating with the PEB383.

0x01 = 1 PCIe lane

R

0x01

03:00

MAX_SPEED

PCIe Maximum Link Speed

This field is always 1 indicating a 2.5-Gbps link.

R

0x1

(Continued)

Bits

Name

Description

Type

Reset value