14. Register Descriptions > Advanced Error Reporting Capability Registers

194

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

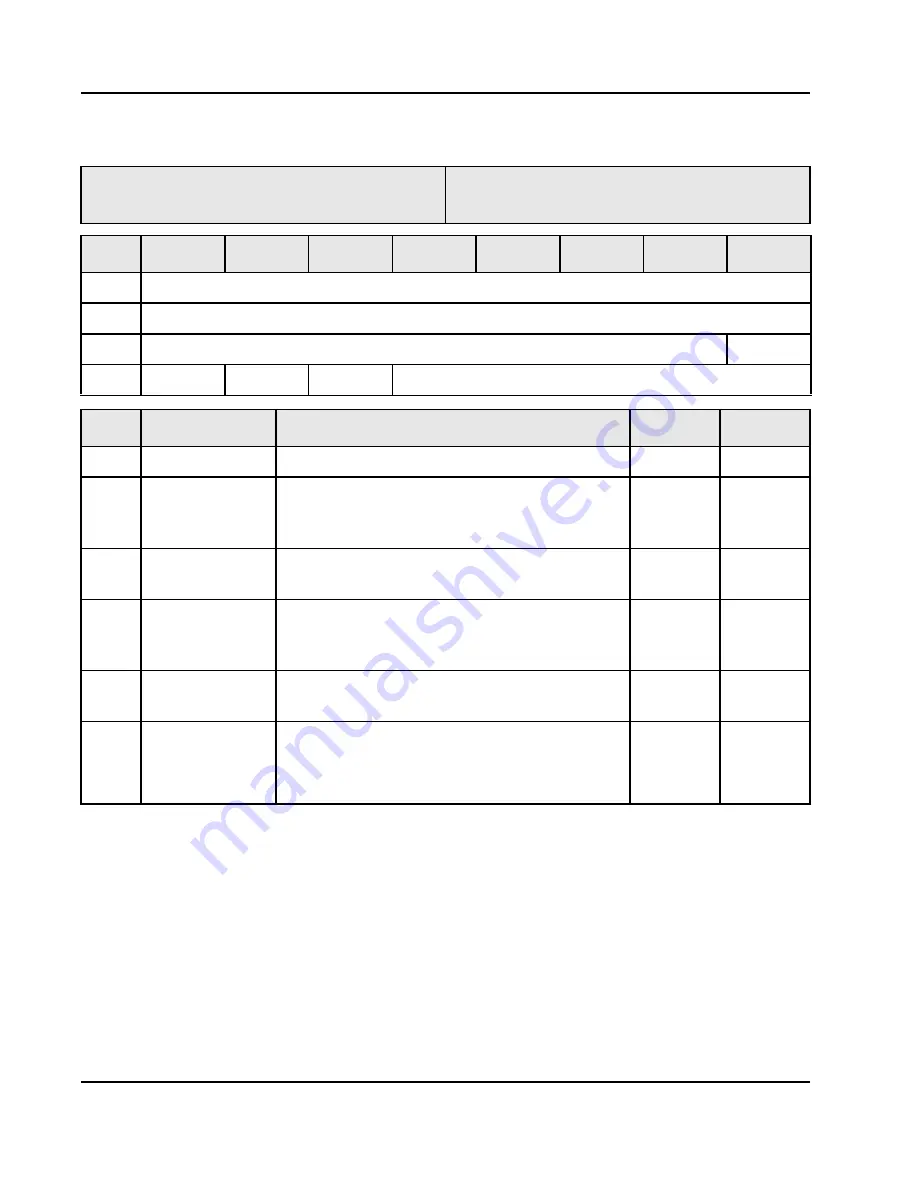

14.8.7

PCIe Advanced Error Capabilities and Control Register

Register name: PCIE_ADV_ERR_CAP_CTRL

Reset value: 0x0000_00A0

Register offset: 0x118

Bits

7

6

5

4

3

2

1

0

31:24

Reserved

23:16

Reserved

15:08

Reserved

EC_EN

07:00

EC_CAP

EG_EN

EG_CAP

ERR_PTR

Bits

Name

Description

Type

Reset value

31:9

Reserved

Reserved

R

0x0000_00

8

EC_EN

ECRC Check Enable

0 = Disable

1 = Enable

R/WS

0

7

EC_CAP

ECRC Check Capable

This bit indicates the PEB383 can check ECRC.

R

1

6

EG_EN

ECRC Generation Enable

0 = Disable

1 = Enable

R/WS

0

5

EG_CAP

ECRC Generation Capable

This bit indicates the PEB383 can generate ECRC.

R

1

4:0

ERR_PTR

First Error Pointer

This pointer is a read-only field that identifies the bit position

of the first error reported in the

.

RS

0