15. Electrical Characteristics > AC Timing Specifications

228

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

7. No test load is necessarily associated with this value.

8. Specified at the measurement point and measured using the clock recovery function specified in Section 4.3.3.2. The test load

in Figure 4-25 should be used as the RX device when taking measurements (also refer to the Receiver compliance eye

diagram shown in Figure 4-26). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI

recovered using the clock recovery function specified in Section 4.3.3.2 must be used as a reference for the eye diagram.

9. The T

RX-EYE-MEDIAN-to-MAX-JITTER

specification ensures a jitter distribution in which the median and the maximum deviation

from the median is less than half of the total 0.64. It should be noted that the median is not the same as the mean. The jitter

median describes the point in time where the number of jitter points on either side is approximately equal as opposed the

averaged time value. The RX UI recovered using the clock recovery function specified in Section 4.3.3.2 must be used as the

reference for the eye diagram. This parameter is measured with the equivalent of a zero jitter reference clock. The T

RX-EYE

measurement is to be met at the target bit error rate. The T

RX-EYE-MEDIAN-to-MAX-JITTER

specification is to be met using the

compliance pattern at a sample size of 1,000,000 UI.

10. For more information on the RX-EYE measurement, see the

PCI Express Jitter and BER

white paper.

11. The receiver input impedance shall result in a differential return loss greater than or equal to 10 dB with a differential test input

signal of no less than 200 mV (peak value, 400mV differential peak to peak) swing around ground applied to D+ and D- lines

and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to

1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for the return loss

measurements is 50 Ohms to ground for both D+ and D- lines (that is, as measured by a Vector Network Analyzer with

50-Ohm probes - see Figure 4-25). Note that the series capacitors C

TX

is optional for the return loss measurement.

12. Impedance during all LTSSM states. When transitioning from a Fundamental Reset to Detect (the initial state of the LTSSM)

there is a 5ms transition time before the Receiver termination values must be met on all un-configured lanes of a port.

13. The RX DC Common Mode Impedance that exists when no power is present or Fundamental Reset is asserted. This helps

ensure that the Receiver Detect circuit does not falsely assume a Receiver is powered on when it is not. This term must be

measured at 200mV above the RX ground.

V

RX-IDLE-DET-DIFFp

Electrical Idle Detect

Threshold

65

-

175

mV

V

RX-IDLE-DET-DIFFp

= 2*|V

RX-D+

-

V

RX-D-

|

Measured at the package pins of the

Receiver.

T

RX-IDLE-DET-DIFF-E

NTERTIME

Unexpected Electrical

Idle Enter Detect

Threshold Integration

Time

-

-

10

ms

An unexpected Electrical Idle

(V

RX-DIFFp-p

< V

RX-IDLE-DET-DIFFp-p

)

must be longer than

T

RX-IDLE-DET-ENTERTIME

to signal an

unexpected idle condition.

L

RX-SKEW

Total Skew

-

-

20

ns

Skew across all lanes on a link. This

includes variation in the length of a

SKP ordered set (for example, COM

and one to five SKP Symbols) at the

RX as well as any delay differences

arising from the interconnect itself.

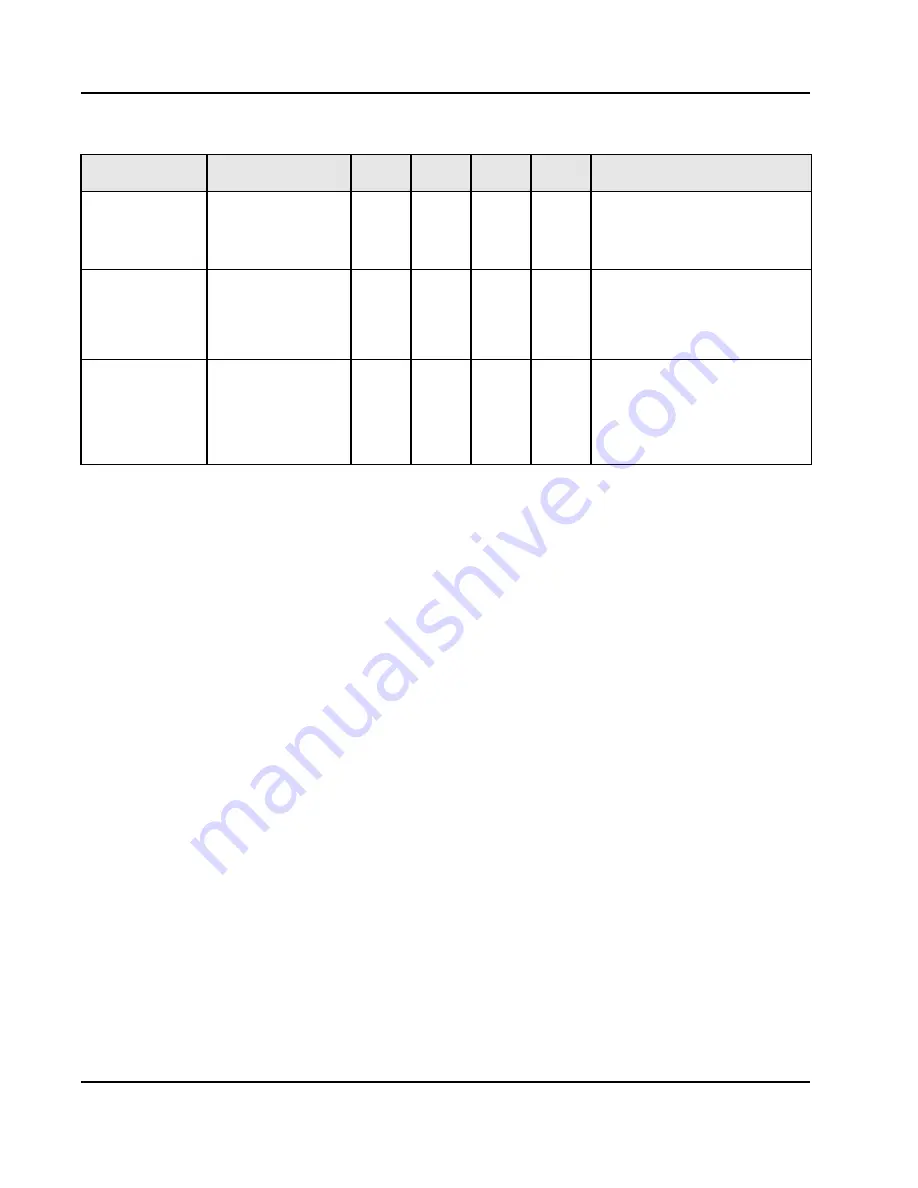

Table 48: PCIe Differential Receiver Input Specifications

(Continued)

Symbol

Parameter

Min.

Nom.

Max.

Units

Comments