14. Register Descriptions > Register Map

147

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

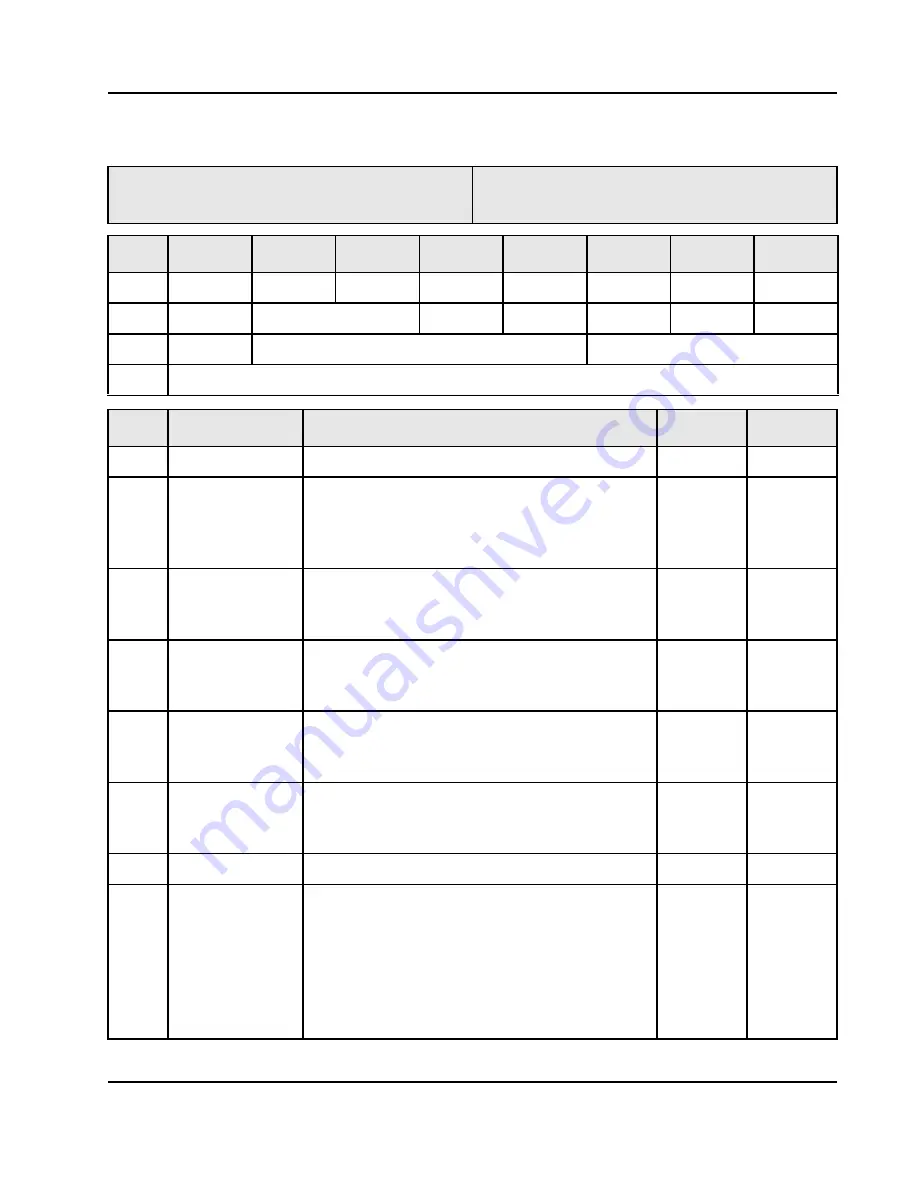

14.3.15

PCI Miscellaneous Control and Status Register

Register name: PCI_MISC_CSR

Reset value: 0x7D10_1900

Register offset: 0x044

Bits

7

6

5

4

3

2

1

0

31:24

Reserved

EN_ARB

EN_ARB3

EN_ARB2

EN_ARB1

EN_ARB0

Reserved

P_ERR

23:16

STC_EN

Reserved

ARB_PRI

ARB_PRI3

ARB_PRI2

ARB_PRI1

ARB_PRI0

15:08

Reserved

CPL_INIT_COUNT

CFG_RT

07:00

Reserved

Bits

Name

Description

Type

Reset value

31

Reserved

Reserved

R

0

30

EN_ARB

Enable Internal Arbiter

This bit enables arbitration for PEB383 requests.

0 = PEB383 disables internal requests.

1 = PEB383 enables internal requests. 0

R/W

1

29

EN_ARB3

Enable Arbiter 3

0 = PEB383 disables PCI_REQ3n for arbitration.

1 = The bridge enables PCI_REQ3n for arbitration.

R/W

1

28

EN_ARB2

Enable Arbiter 2

0 = PEB383 disables PCI_REQ2# for arbitration.

1 = PEB383 enables PCI_REQ2# for arbitration.

R/W

1

27

EN_ARB1

Enable Arbiter 1

0 = PEB383 disables PCI_REQ1# for arbitration.

1 = PEB383 enables PCI_REQ1# for arbitration.

R/W

1

26

EN_ARB0

Enable Arbiter 0

0 = PEB383 disables PCI_REQ0# for arbitration.

1 = PEB383 enables PCI_REQ0# for arbitration.

R/W

1

25

Reserved

Reserved

R

0

24

P_ERR

Parity Error Behavior

This bit controls the behavior of the PEB383 when it detects

a data parity error during a non-posted write transaction.

0 = PCI_PERRn is asserted and the corrupted data is

passed.

1 = PCI_PERRn is asserted and the transaction is asserted

on the originating bus, appropriate status bits are set,

data is discarded, and the request is not enqueued.

R

1