1. Functional Overview > Typical Applications

10

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

A read initiated on the PCI bus that is decoded for an upstream target is handled as a delayed

transaction by the PEB383. The bridge latches the read transaction and attempts to reserve buffer space

in its upstream read completion buffer. If space is successfully reserved in the buffer, the PEB383

initiates a read on the PCIe Interface. When the read data is returned from the root complex, it is stored

in the upstream read completion buffer. PCI-initiated reads, however, do not define the amount of data

to read. Once the master on the PCI bus retries the read transaction, the transaction is checked to

determine if the read data is returned. If it has the read data, the PEB383 responds as the target and

transfers the read data to the PCI bus. Note the upstream read completion buffer is not a simple FIFO,

as the order that masters on the PCI bus retry is not deterministic. If the completion buffer becomes

empty prior to the transaction completing, the PEB383 disconnects from the PCI bus. When the read

transaction is completed, the PEB383 discards any prefetched data that is not used and frees up the

buffer. The maximum number of outstanding read requests per master is controlled by DTL[7:0] bits in

“Secondary Retry Count Register”

.

A write initiated on the PCIe Interface with the target on the downstream PCI bus is written into the

downstream posted write buffer. The PEB383 acts as the master for the transaction and arbitrates for

the PCI bus and initiates the write transaction. The downstream posted write buffer is managed as a

FIFO. There will always be space available in the buffer to accept packet data because of the flow

control method used by the PCIe data link layer. If the downstream posted write buffer is about to

overflow, the upstream device will be informed of this by its lack of credits and will not send any more

write data to the PEB383.

A read initiated on the PCIe Interface with the target on the downstream PCI bus is written into the

downstream read request queue. The downstream read request queue is managed with flow control

credits to prevent overflowing. The PEB383 latches the read transaction and attempts to reserve space

in the downstream read completion buffer. If space is successfully reserved in the buffer, the PEB383

acts as the master for the transaction and initiates a read transaction on the PCI bus.Programmable

address decoders instruct the PEB383 which transactions on the PCI bus to forward upstream, and

which transactions on the PCIe link to forward downstream.

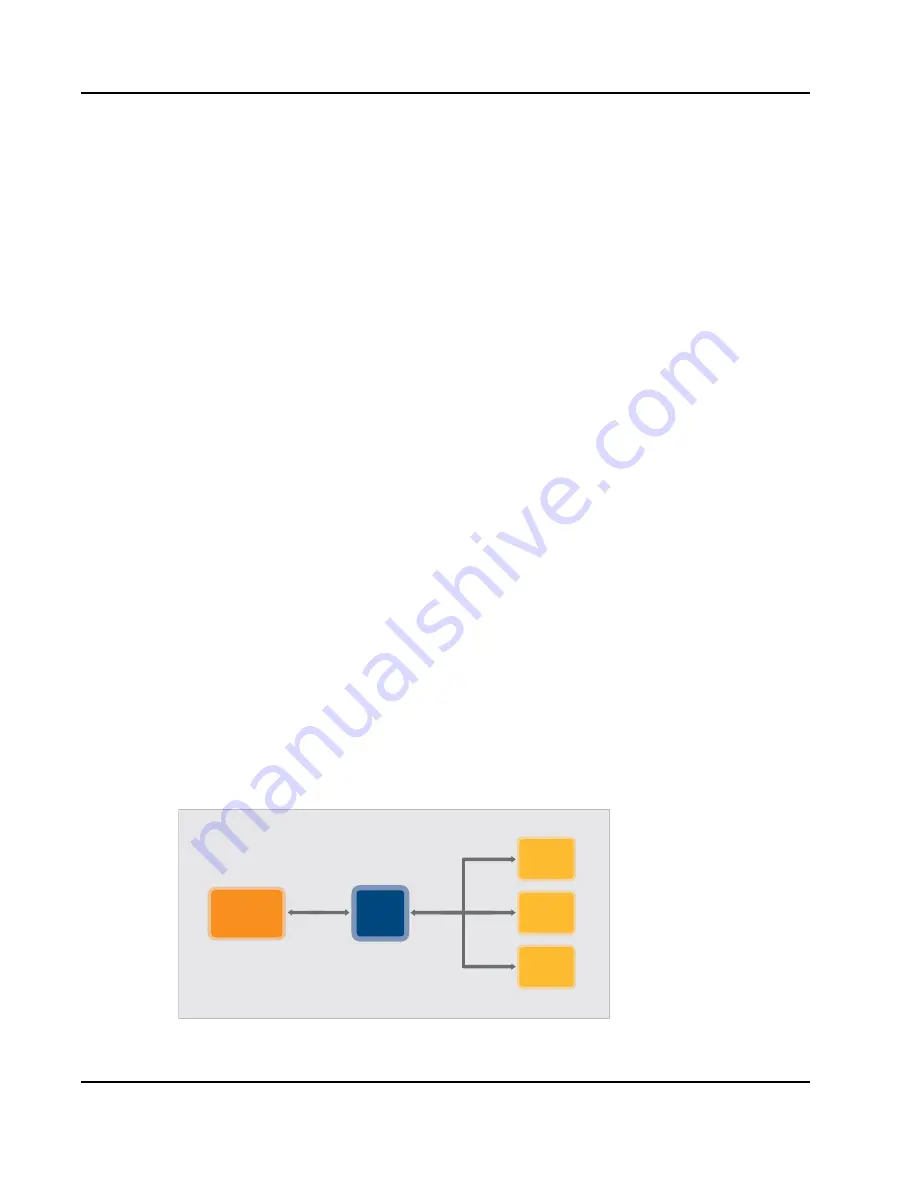

1.4

Typical Applications

This section illustrates some typical applications for the PEB383.

Figure 3: Network Interface Card Application

80E2000_TA001_01

32-bit,

66-MHz

PCI

x1 PCIe

PEB383

Integrated

CPU

FE

USB

GbE