IDT Transparent Mode Operation

Generic PCI to PCI Bridge Register Definition

PES12N3 User Manual

9 - 34

June 7, 2006

Notes

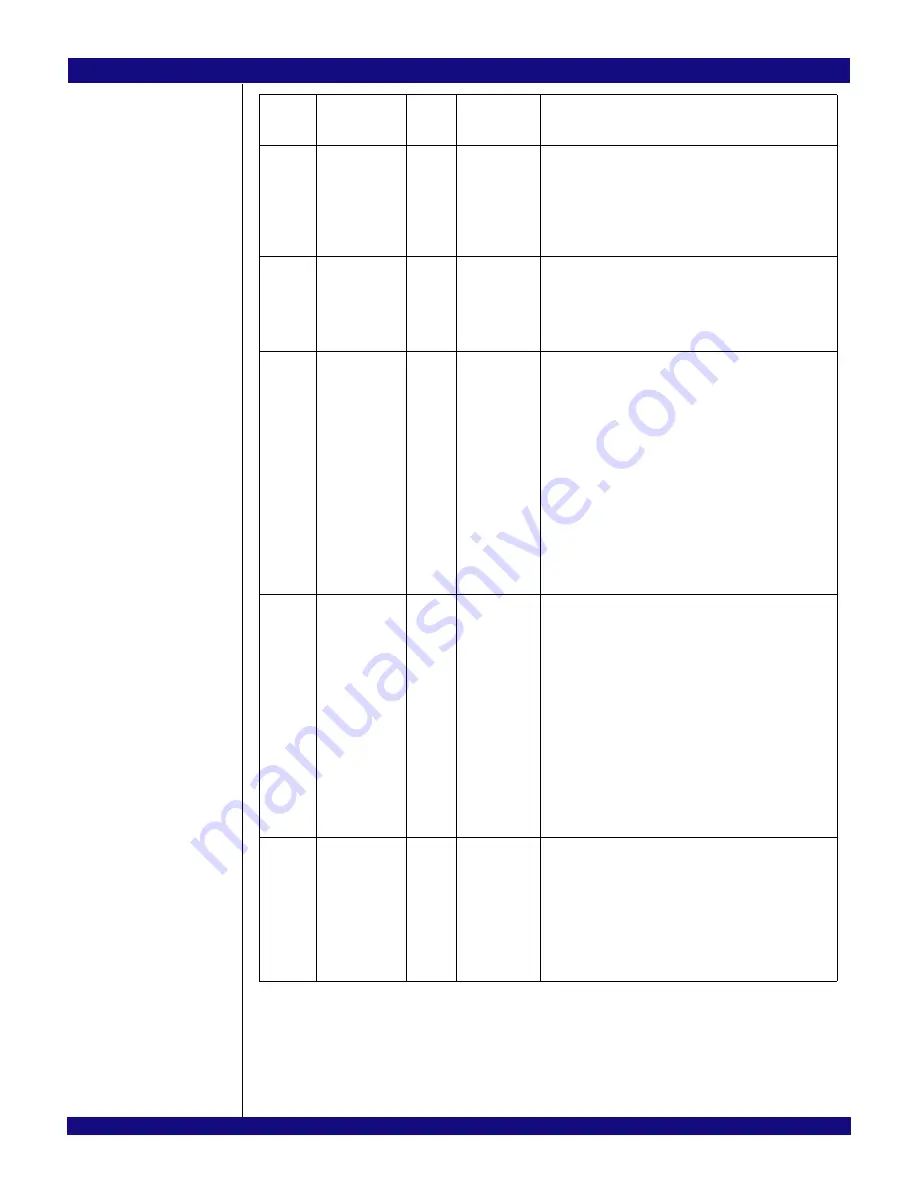

4

CCIE

RW

0x0

Command Complete Interrupt Enable. This bit when set

enables the generation of a Hot-Plug interrupt when a com-

mand is completed by the Hot-Plug Controller.

This bit is read-only and has a value of zero when the cor-

responding capability is not enabled in the PCIESCAP reg-

ister.

5

HPIE

RW

0x0

Hot Plug Interrupt Enable. This bit when set enables gen-

eration of a Hot-Plug interrupt on enabled Hot-Plug events.

This bit is read-only and has a value of zero when the cor-

responding capability is not enabled in the PCIESCAP reg-

ister.

7:6

AIC

RW

0x3

Attention Indicator Control. When read, this register

returns the current state of the Attention Indicator. Writing

to this register sets the indicator and causes the port to

send the appropriate ATTENTION_INDICATOR_* mes-

sage.

This bit is read-only and has a value of zero when the cor-

responding capability is not enabled in the PCIESCAP reg-

ister.

This field is always zero if the ATTIP bit is cleared in the

PCIESCAP register.

0x0 -(reserved) Reserved

0x1 -(on) On

0x2 -(blink) Blink

0x3 -(off) Off

9:8

PIC

RW

0x1

Power Indicator Control. When read, this register returns

the current state of the Power Indicator. Writing to this reg-

ister sets the indicator and causes the port to send the

appropriate POWER_INDICATOR_* message.

This bit is read-only and has a value of zero when the cor-

responding capability is not enabled in the PCIESCAP reg-

ister.

This field is always zero if the PWRIP bit is cleared in the

PCIESCAP register.

0x0 -(reserved) Reserved

0x1 -(on) On

0x2 -(blink) Blink

0x3 -(off) Off

This field has no effect on the upstream port.

10

PCC

RW

0x0

Power Controller Control. When read, this register

returns the current state of the power applied to the slot.

Writing to this register sets the power state of the slot.

This bit is read-only and has a value of zero when the cor-

responding capability is not enabled in the PCIESCAP reg-

ister.

0x0 -(on) Power on

0x1 -(off) Power off

Bit

Field

Field

Name

Type

Default

Value

Description

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...