IDT Transparent Mode Operation

Generic PCI to PCI Bridge Register Definition

PES12N3 User Manual

9 - 56

June 7, 2006

Notes

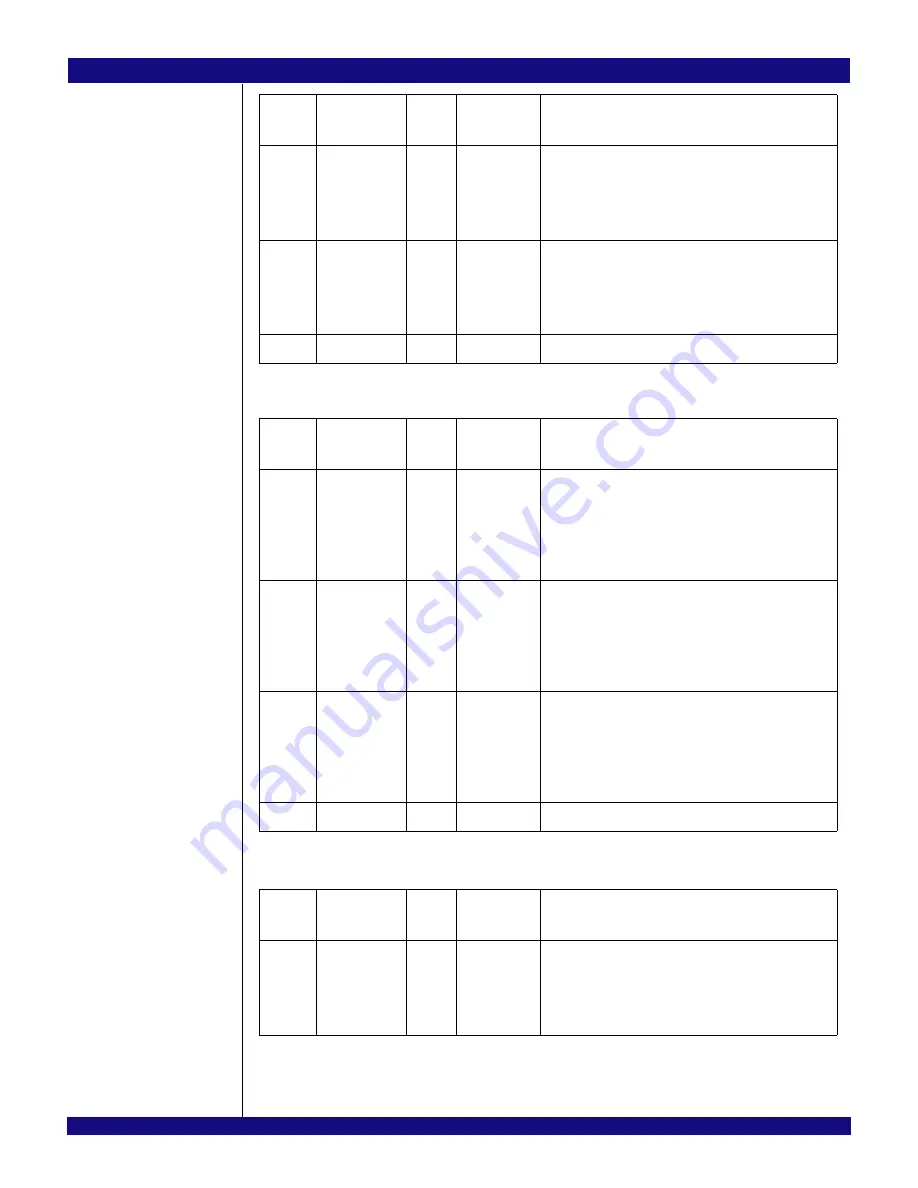

TMFSTS - Test Mode Fail Status (0x0C0)

TMSSTS - Test Mode Synchronization Status (0x0C4)

25

TXRS

RW

0x0

Transmit Re-Sync. Writing a one to this bit position while

the PES12N3 is in a test mode that requires synchroniza-

tion, causes the PRBS or pattern generator on each lane to

start a synchronization sequence.

This field always returns a value of zero when read.

26

RXRS

RW

0x0

Receive Re-Sync. Writing a one to this bit position while

the PES12N3 is in a test mode that requires synchroniza-

tion, causes the PRBS or pattern checker on each lane to

start a synchronization sequence.

This field always returns a value of zero when read.

31:27

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

7:0

PATF

RW1C

0x0

Port A Test Failure. Each bit in this field corresponds to a

port lane (e.g., bit zero corresponds to lane zero of the

port). When the switch is configured to operate in a SerDes

test mode, the lane is enabled in the TMCTL register, and

an error is detected on a lane, then the corresponding bit in

this field is set.

15:8

PBTF

RW1C

0x0

Port B Test Failure. Each bit in this field corresponds to a

port lane (e.g., bit zero corresponds to lane zero of the

port). When the switch is configured to operate in a SerDes

test mode, the lane is enabled in the TMCTL register, and

an error is detected on a lane, then the corresponding bit in

this field is set.

23:16

PCTF

RW1C

0x0

Port C Test Failure. Each bit in this field corresponds to a

port lane (e.g., bit zero corresponds to lane zero of the

port). When the switch is configured to operate in a SerDes

test mode, the lane is enabled in the TMCTL register, and

an error is detected on a lane, then the corresponding bit in

this field is set.

31:24

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

7:0

PASA

RW1C

0x0

Port A Synchronization Achieved. Each bit in this field

corresponds to a port lane (e.g., bit zero corresponds to

lane zero of the port). When the lane is enabled in the

TMCTL register, and synchronization has been achieved,

then the corresponding bit in this field is set.

Bit

Field

Field

Name

Type

Default

Value

Description

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...