IDT Transparent Mode Operation

Downstream Port C Configuration Space Registers

PES12N3 User Manual

9 - 14

June 7, 2006

Notes

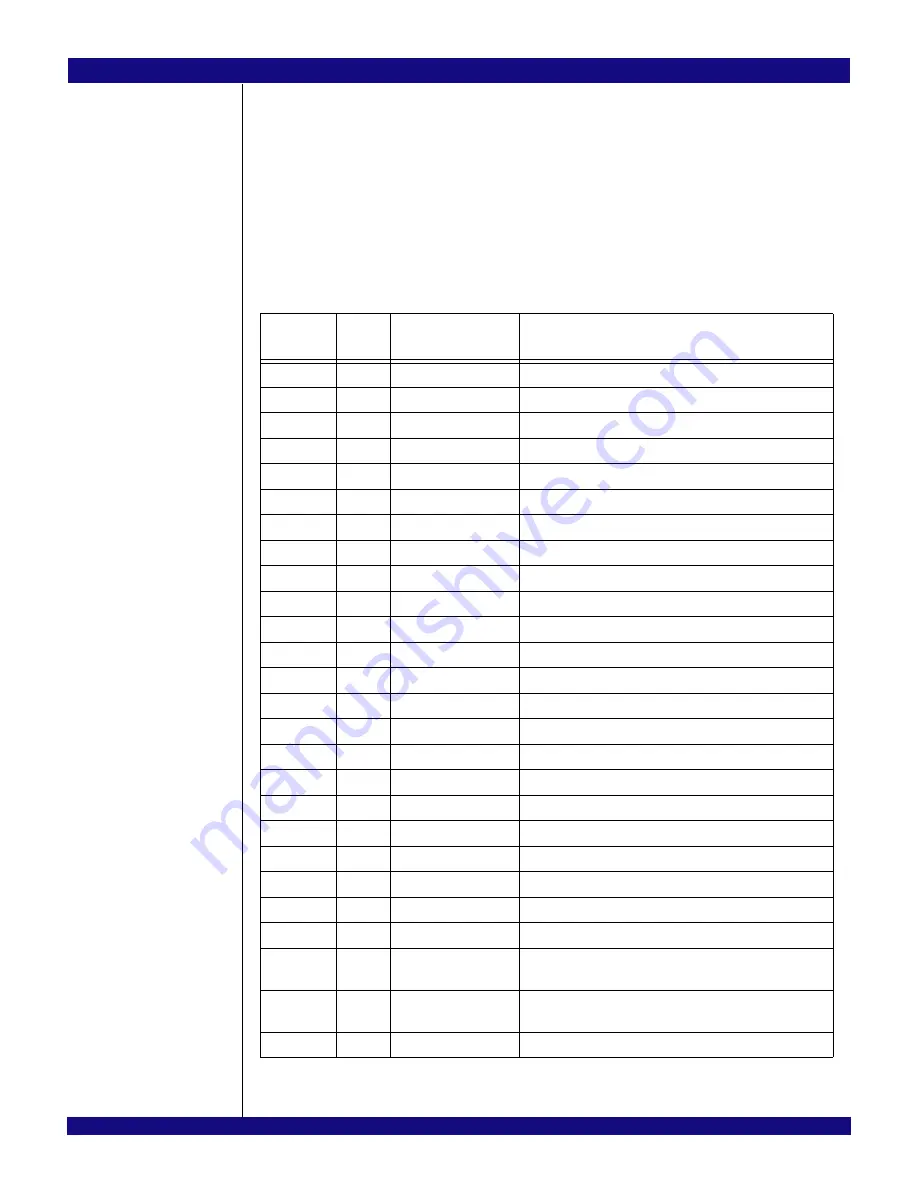

Downstream Port C Configuration Space Registers

All configuration space locations not listed in Table 9.8 return a value of zero when read. Writes to these

locations are ignored and have no side-effects.

Port C configuration space registers may be read and written via the slave SMBus interface and initial-

ized from the serial EEPROM using the CSR system address formed by adding the base address 0x2000

to the PCI configuration space offset address.

Note: In pdf format, clicking on a register name in the Register Definition column creates a jump

to the appropriate register. To return to the starting place in this table, click on the same register

name (in blue) in the register section.

Cfg.

Offset

Size

Register

Mnemonic

Register Definition

0x000

Word

PC_VID

VID - Vendor Identification (0x000) on page 9-17

0x002

Word

PC_DID

DID - Device Identification (0x002) on page 9-17

0x004

Word

PC_PCICMD

PCICMD - PCI Command (0x004) on page 9-17

0x006

Word

PC_PCISTS

PCISTS - PCI Status (0x006) on page 9-18

0x008

Byte

PC_RID

RID - Revision Identification (0x008) on page 9-19

0x009

3 Bytes

PC_CCODE

CCODE - Class Code (0x009) on page 9-19

0x00C

Byte

PC_CLS

CLS - Cache Line Size (0x00C) on page 9-20

0x00D

Byte

PC_PLTIMER

PLTIMER - Primary Latency Timer (0x00D) on page 9-20

0x00E

Byte

PC_HDR

HDR - Header Type Register (0x00E) on page 9-20

0x00F

Byte

PC_BIST

BIST - Built-in Self Test (0x00F) on page 9-20

0x010

DWord

PC_BAR0

BAR0 - Base Address Register 0 (0x010) on page 9-20

0x014

DWord

PC_BAR1

BAR1 - Base Address Register 1 (0x014) on page 9-20

0x018

Byte

PC_PBUSN

PBUSN - Primary Bus Number (0x018) on page 9-21

0x019

Byte

PC_SBUSN

SBUSN - Secondary Bus Number (0x019) on page 9-21

0x01A

Byte

PC_SUBUSN

SUBUSN - Subordinate Bus Number (0x01A) on page 9-21

0x01B

Byte

PC_SLTIMER

SLTIMER - Secondary Latency Timer (0x01B) on page 9-21

0x01C

Byte

PC_IOBASE

IOBASE - I/O Base (0x01C) on page 9-21

0x01D

Byte

PC_IOLIMIT

IOLIMIT - I/O Limit (0x01D) on page 9-22

0x01E

Word

PC_SECSTS

SECSTS - Secondary Status (0x01E) on page 9-22

0x020

Word

PC_MBASE

MBASE - Memory Base (0x020) on page 9-23

0x022

Word

PC_MLIMIT

MLIMIT - Memory Limit (0x022) on page 9-23

0x024

Word

PC_PMBASE

PMBASE - Prefetchable Memory Base (0x024) on page 9-23

0x026

Word

PC_PMLIMIT

PMLIMIT - Prefetchable Memory Limit (0x026) on page 9-24

0x028

DWord

PC_PMBASEU

PMBASEU - Prefetchable Memory Base Upper (0x028) on

page 9-24

0x02C

DWord

PC_PMLIMITU

PMLIMITU - Prefetchable Memory Limit Upper (0x02C) on

page 9-24

0x030

Word

PC_IOBASEU

IOBASEU - I/O Base Upper (0x030) on page 9-24

Table 9.8 Downstream Port C Configuration Space Registers (Part 1 of 3)

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...