IDT Transparent Mode Operation

Generic PCI to PCI Bridge Register Definition

PES12N3 User Manual

9 - 18

June 7, 2006

Notes

6

PERRE

RW

0x0

Parity Error Enable. The Master Data Parity Error bit is

set in the PCI Status register (PCISTS) if this bit is set and

the bridge receives a poisoned completion or a poisoned

write. If this bit is cleared, then the Master Data Parity Error

bit in the PCI Status register is never set.

0x0 - (disable) Disable Master Parity Error bit reporting.

0x1 - (enable) Enable Master Parity Error bit reporting.

7

ADSTEP

RO

0x0

Address Data Stepping. Not applicable.

8

SERRE

RW

0x0

SERR Enable. Non-fatal and fatal errors detected by the

bridge are reported to the Root Complex when this bit is set

or the bits in the PCI Express Device Control register are

set (see PCIEDCTL - PCI Express Device Control

(0x048)).

0x0 - (disable) Disable non-fatal and fatal error reporting

if also disabled in Device Control register.

0x1 - (enable) Enable non-fatal and fatal error reporting.

9

FB2B

RO

0x0

Fast Back-to-Back Enable. Not applicable.

10

INTXD

RW

0x0

INTx Disable. Controls the ability of the PCI-PCI bridge to

generate an INTx interrupt message.

15:11

Reserved

RO

0x0

Reserved field.

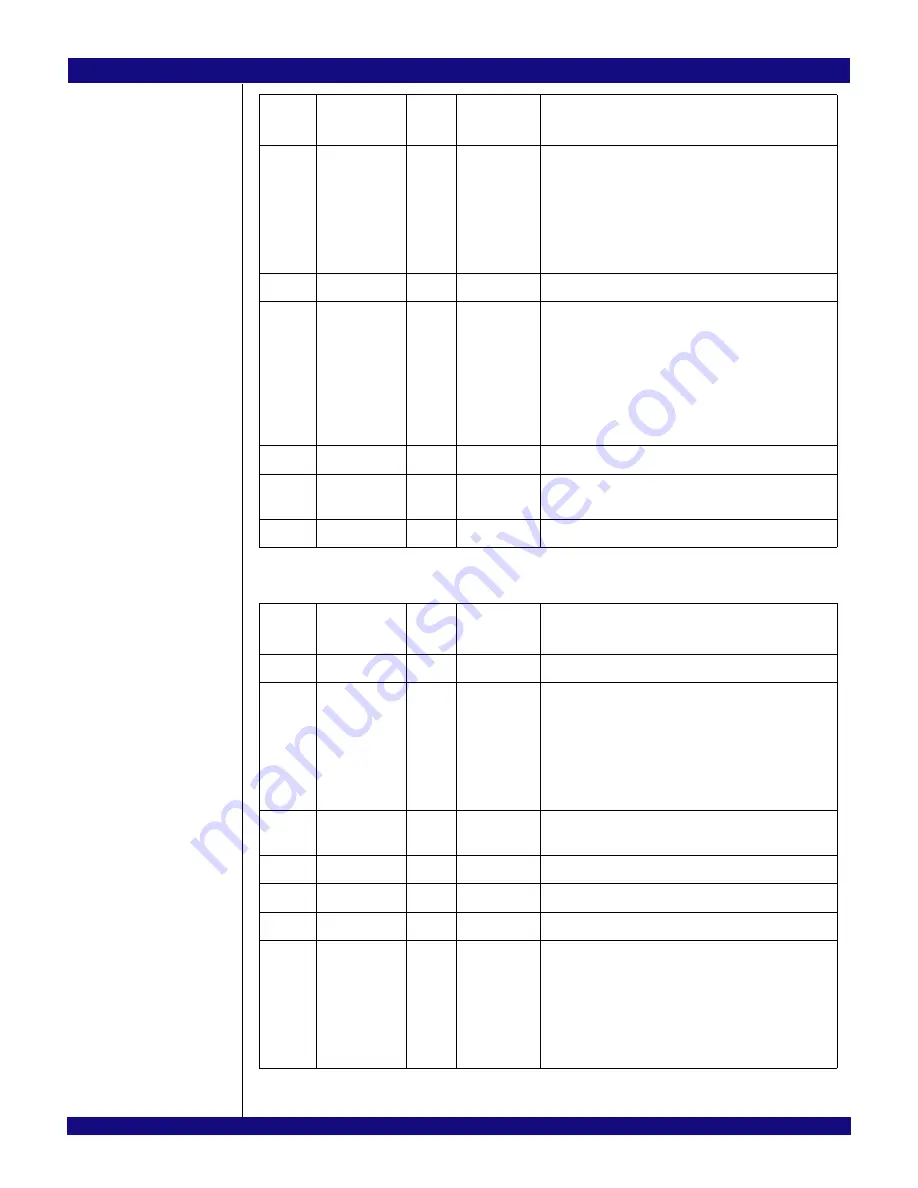

Bit

Field

Field

Name

Type

Default

Value

Description

2:0

Reserved

RO

0x0

Reserved.

3

INTS

RO

0x0

INTx Status. This bit is set when an INTx interrupt is pend-

ing from the device.

INTx emulation interrupts forwarded by switch ports from

devices downstream of the bridge are not reflected in this

bit. For ports B and C, this bit is set if an interrupt has been

“asserted” by the corresponding port’s hot-plug controller.

For port A, this field is always zero.

4

CAPL

RO

0x1

Capabilities List. This bit is hardwired to one to indicate

that the bridge implements an extended capability list item.

5

C66MHZ

RO

0x0

66 MHz Capable. Not applicable.

6

Reserved

RO

0x0

Reserved.

7

FB2B

RO

0x0

Fast Back-to-Back (FB2B). Not applicable.

8

MDPED

RW1C

0x0

Master Data Parity Error Detected. This bit is set when

the PERRE bit is set in the PCI Command register and the

bridge receives a poisoned completion or poisoned write

request on the primary side of the bridge.

0x0 - (noerror) no error.

0x1 - (error) Poisoned write request or completion

received on primary side.

Bit

Field

Field

Name

Type

Default

Value

Description

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...