IDT Transparent Mode Operation

Generic PCI to PCI Bridge Register Definition

PES12N3 User Manual

9 - 46

June 7, 2006

Notes

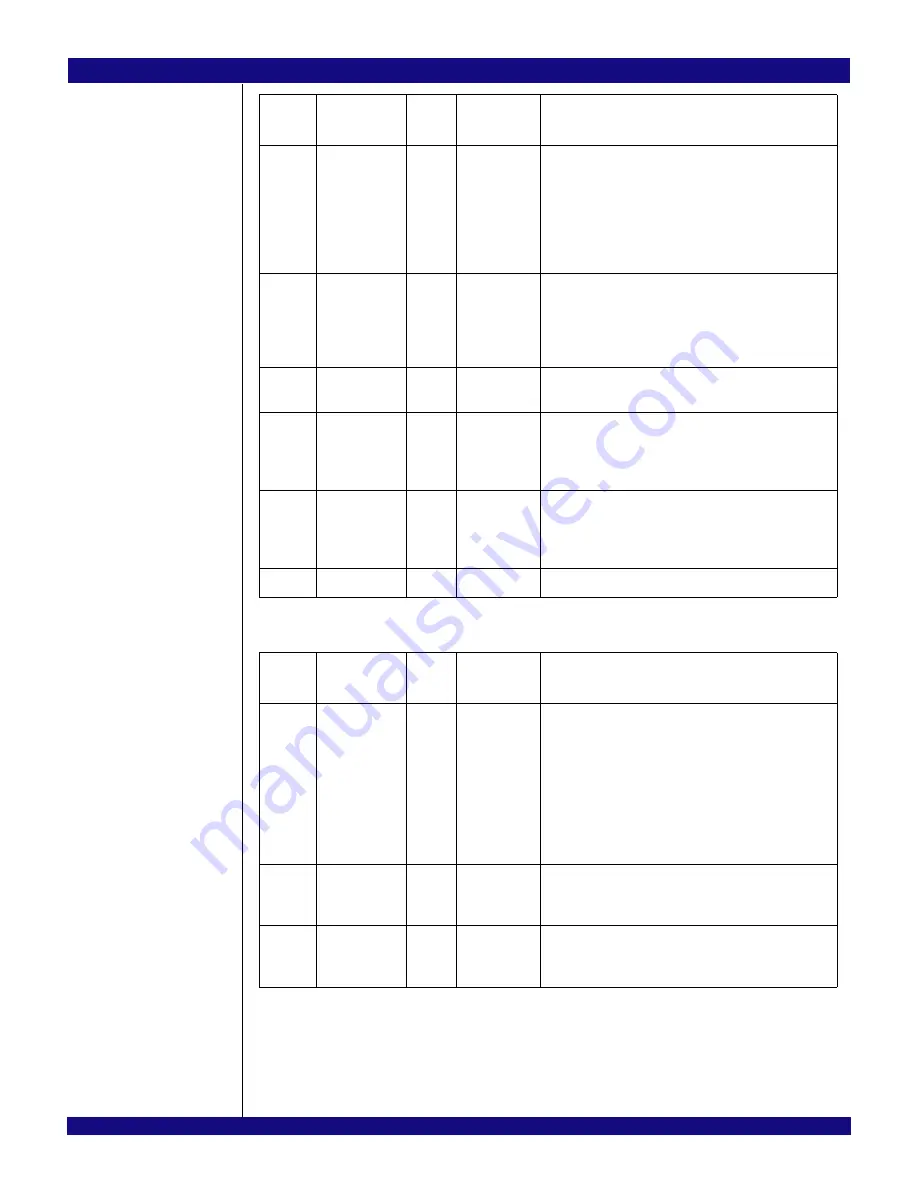

SMBUSCTL - SMBus Control (0x0B0)

25

NAERR

RW1C

0x0

No Acknowledge Error. This bit is set if an unexpected

NACK is observed during a master SMBus transaction.

The setting of this bit may indicate the following: that the

addressed device does not exist on the SMBus (i.e.,

addressing error); data is unavailable or the device is busy;

an invalid command was detected by the slave; or invalid

data was detected by the slave.

26

LAERR

RW1C

0x0

Lost Arbitration Error. When the master SMBus interface

loses arbitration for the SMBus, it automatically re-arbi-

trates for the SMBus. If the master SMBus interface loses

16 consecutive arbitration attempts, then the transaction is

aborted and this bit is set.

27

OTHERERR

RW1C

0x0

Other Error. This bit is set if a misplaced START or STOP

condition is detected by the master SMBus interface.

28

ICSERR

RW1C

0x0

Initialization Checksum Error. This bit is set if an invalid

checksum is computed during Serial EEPROM initialization

or when a configuration done command is not found in the

serial EEPROM.

29

URIA

RW1C

0x0

Unmapped Register Initialization Attempt. This bit is set

if an attempt is made to initialize via serial EEPROM a reg-

ister that is not defined in the corresponding PCI configura-

tion space.

31:30

Reserved

RO

0x0

Reserved field.

Bit

Field

Field

Name

Type

Default

Value

Description

15:0

MSMBCP

RW

HWINIT

Master SMBus Clock Prescalar. This field contains a

clock prescalar value used during master SMBus transac-

tions. The prescalar clock period is equal to 32 ns multi-

plied by the value in this field. When the field is cleared to

zero or one, the clock is stopped.

The initial value of this field is 0x0139 when the master

SMBus is configured to operate in slow mode (i.e., 100

KHz) in the boot configuration and to 0x0053

1

when it is

configured to operate in fast mode (i.e., 400 KHz).

16

MSMBIOM

RW

0x0

Master SMBus Ignore Other Masters. When this bit is

set, the master SMBus proceeds with transactions regard-

less of whether it won or lost arbitration.

17

ICHECKSUM

RW

0x0

Ignore Checksum Errors. When this bit is set, serial

EEPROM initialization checksum errors are ignored (i.e.,

the checksum always passes).

Bit

Field

Field

Name

Type

Default

Value

Description

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...