IDT PES12N3 Device Overview

Introduction

PES12N3 User Manual

1 - 2

June 7, 2006

Notes

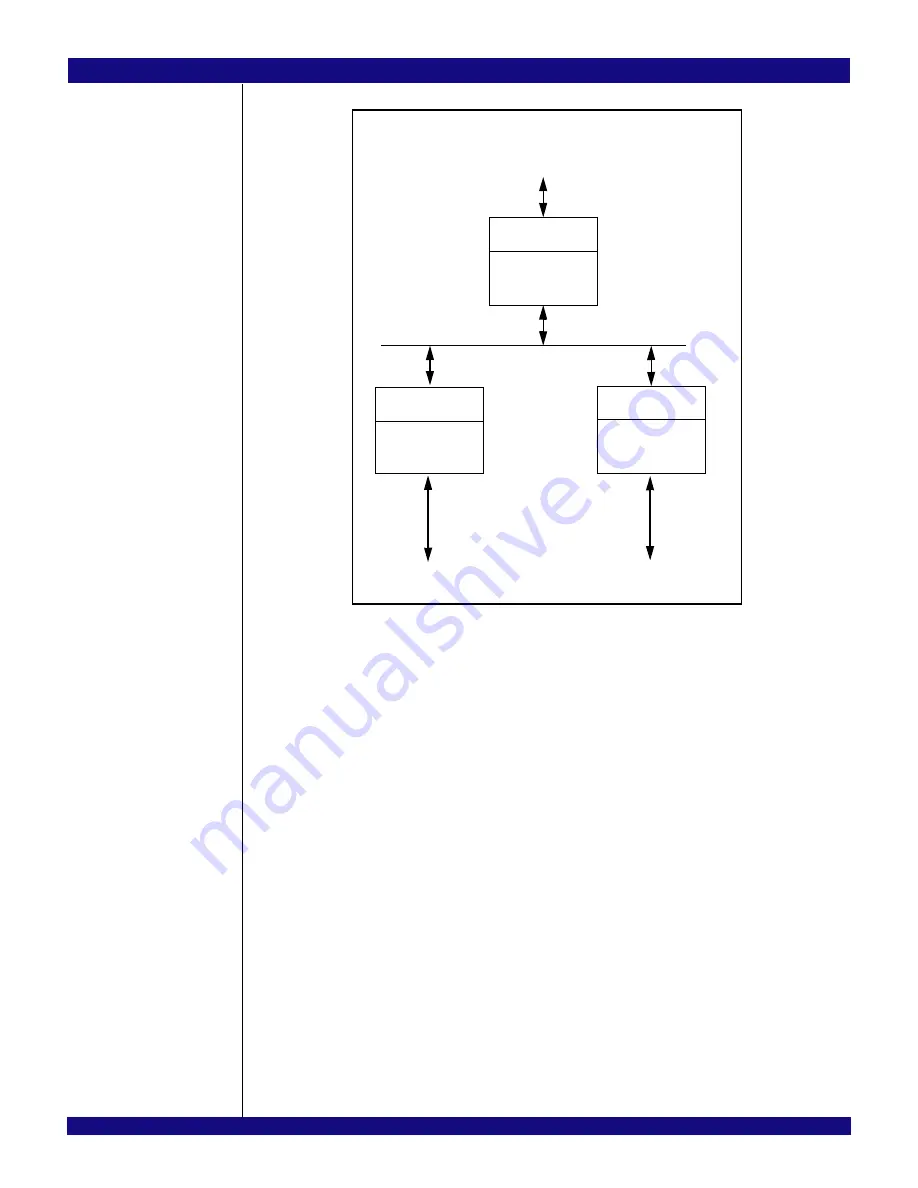

Figure 1.1 PES12N3 Functional Block Diagram

As shown in Figure 1.1, port A is configured as the upstream port and ports B and C as the downstream

ports. Port B resides on the internal PCI Bus at Device 0, Function 0. Port C resides on the internal PCI Bus

at Device 1, Function 0.

Type 1

Configuration Header

PCI-PCI

Transparent

Bridge

Type 1

Configuration Header

PCI-PCI

Transparent Bridge

(Device 1)

Virtual PCI Bus

Port A

(Upstream Port)

Port B

(Downstream Port)

Port C

(Downstream Port)

Type 1

Configuration Header

PCI-PCI

Transparent Bridge

(Device 0)

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...