3. Processor Bus Interface

102

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

3.4.1.2

Address Translation

The address generated by the PB Master is dependent on the use of address translation in the source

target image (see

“PCI-1 Target Image x Control Register” on page 268

. When address translation is

enabled

—

TA_EN bit is set in the PCI target image

—

PowerSpan II produces the processor bus

address using three inputs:

•

the incoming address from the source bus

•

the block size of the target image

•

the translation offset

This does not apply to DMA transfers because the destination address is assumed to have the necessary

offset by design.

For more information, see

“DMA x Destination Address Register” on page 310

.

3.4.1.3

Transaction type

The transfer type parameter of a PB master transaction, PB_TT, is specified with the PCI target image

or DMA channel registers. The following registers control the parameter for write transactions:

•

WTT[4:0] field in the

“PCI-1 Target Image x Control Register” on page 268

•

WTT[4:0] field in the

“DMA x Attributes Register” on page 317

The following registers control the parameter for read transactions:

•

RTT[4:0] field in the

“PCI-1 Target Image x Control Register” on page 268

•

RTT[4:0] field in the

“DMA x Attributes Register” on page 317

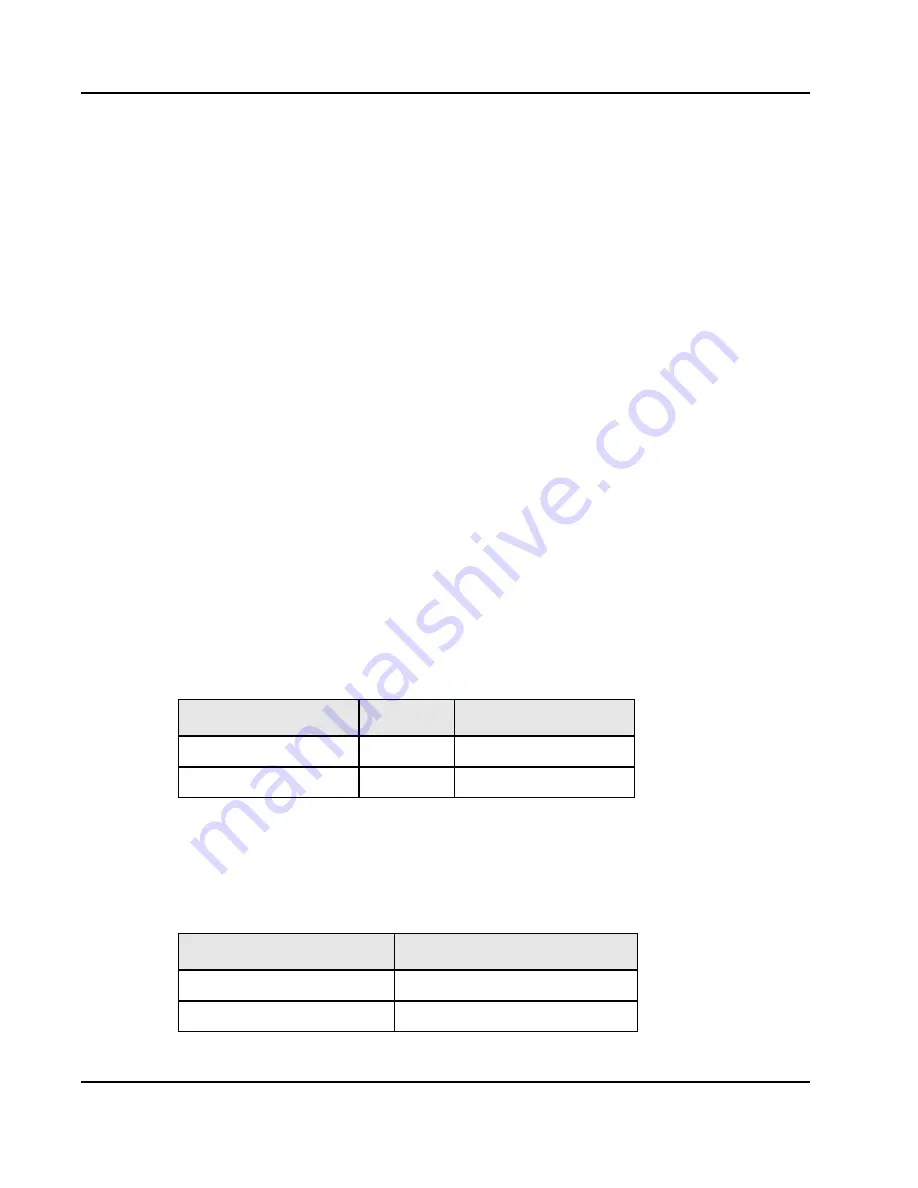

The default transfer type generated by the PowerSpan II PB Interface master is shown in

3.4.1.4

Address Parity

Address parity generation is provided on each byte of the address bus. Address parity bit assignments

are defined in

Table 20: Default PowerSpan II PB Master Transfer Type

PB Master Transaction

PB_TT[0:4]

Processor Bus Command

Writes

00010

Write with flush

Reads

01010

Read

Table 21: PowerSpan II PB Address Parity Assignments

Address Bus

Address Parity

PB_A[0:7]

PB_AP[0]

PB_A[8:15]

PB_AP[1]