5. I2C/EEPROM

130

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

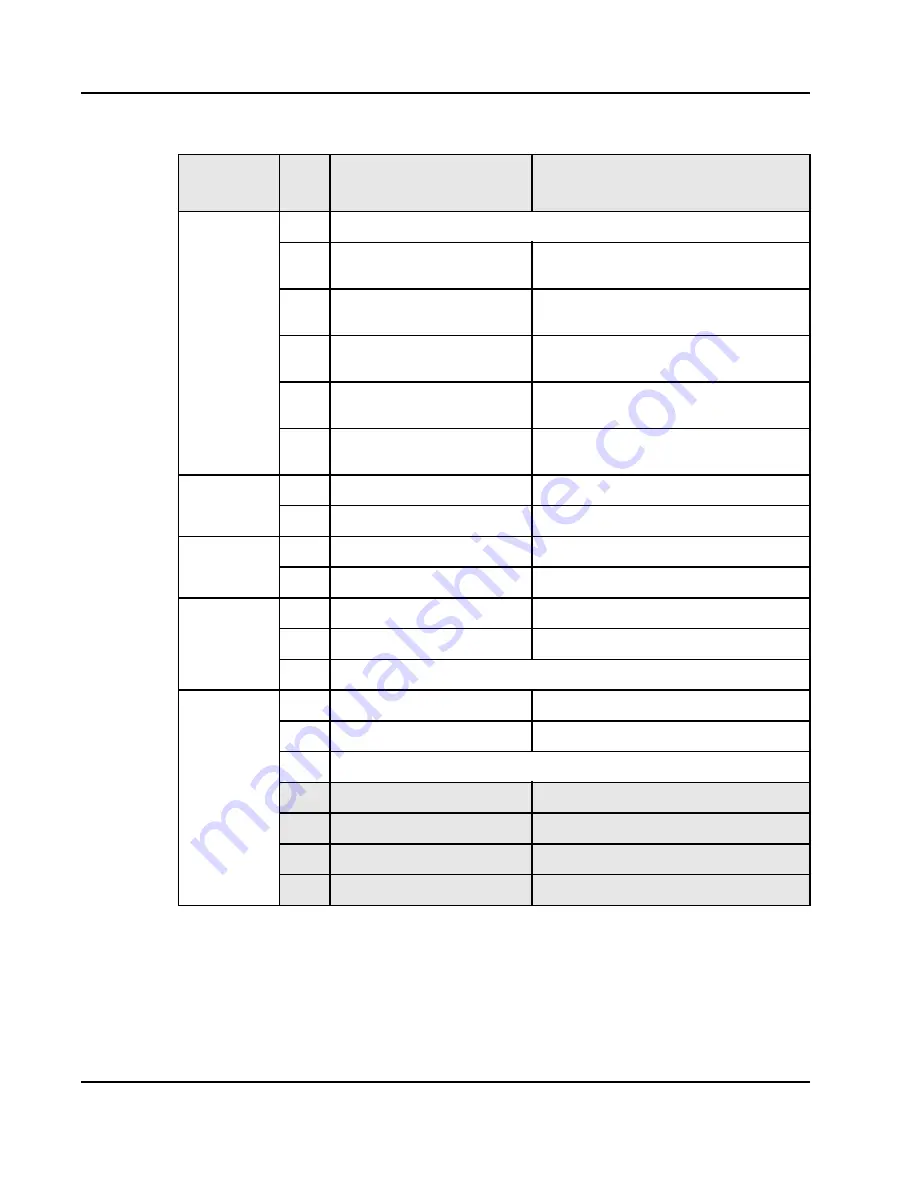

0x0C

7-5

PowerSpan II Reserved

4

P1_MISC_CSR[BSREG_BAR_E

N]

PCI-1 Register image base address register

enable

3

P1_TI0_CTL[BAR_EN]

PCI-1 Target image 0 base address register

enable

2

P1_TI1_CTL[BAR_EN]

PCI-1 Target image 1 base address register

enable

1

P1_TI2_CTL[BAR_EN]

PCI-1 Target image 2 base address register

enable

0

P1_TI3_CTL[BAR_EN]

PCI-1 Target image 3 base address register

enable

0x0D

7-4

P1_TI0_CTL[BS]

PCI-1 Target image 0 block size

3-0

P1_TI1_CTL[BS]

PCI-1 Target image 1 block size

0x0E

7-4

P1_TI2_CTL[BS]

PCI-1 Target image 2 block size

3-0

P1_TI3_CTL[BS]

PCI-1 Target image 3 block size

0x0F

7

MISC_CSR[VPD_EN]

PCI Vital Product Data enable

6-4

MISC_CSR[VPD_CS[2:0]]

PCI Vital Product Data chip select

3-0

PowerSpan II Reserved

0x10

7

MISC_CSR[P1_LOCKOUT]

PCI-1 Lockout

6

MISC_CSR[P2_LOCKOUT]

PCI-2 Lockout

5-4

PowerSpan II Reserved

3

MISC_CSR[PCI_ARB_CFG]

PCI Arbiter Configuration Complete

2

MISC_CSR[PCI_M7]

PCI Arbiter Master 7

1

MISC_CSR[PCI_M6]

PCI Arbiter Master 6

0

MISC_CSR[PCI_M5]

PCI Arbiter Master 5

Table 31: Power-up EEPROM Load Sequence

Byte

Offset

Bit

Name

Description