6. Arbitration

138

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

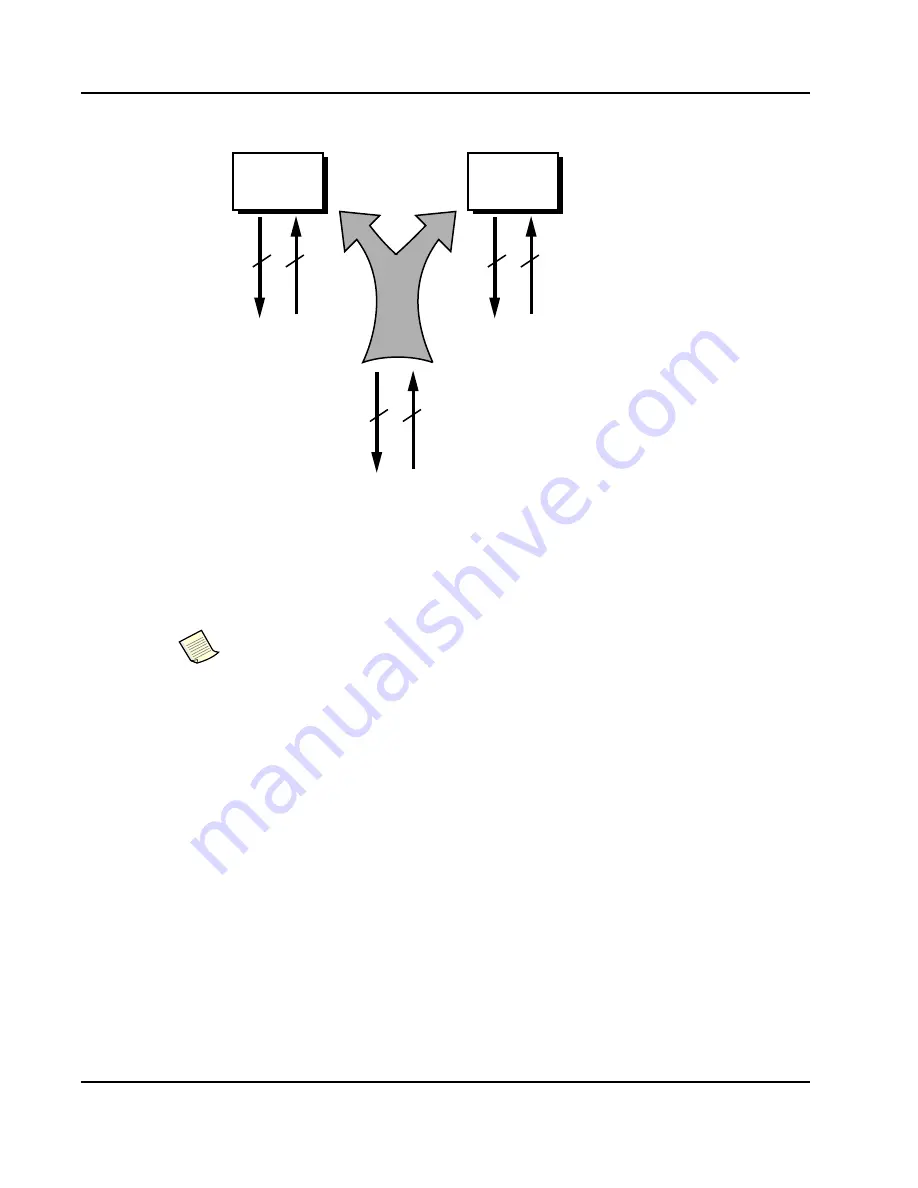

Figure 20: Assignment of Additional Bus Requesters with PCI Arbiters

6.2.1

Arbitration Levels

The PowerSpan II PCI arbiter implements a fairness algorithm in order to prevent deadlocks. There are

two priority levels signed to the PCI master agents. Fairness is defined by the

PCI 2.2 Specification

as

an algorithm that grants all potential PCI masters access to the bus, independent of other requests.

6.2.1.1

High and Low Priority PCI Agents

There are two priority levels assigned to the PCI Master Agents: high priority and low priority. Each

priority level performs a round-robin arbitration algorithm among the PCI masters assigned to each

level. For example, all the PCI masters assigned to the lower priority level represent one entry in the

higher priority round-robin arbitration. For every turn of the high priority round-robin arbitration, high

priority PCI masters asserting Px_REQ# are granted access to the PCI bus. At the same time, only one

lower priority level PCI master asserting Px_REQ# is granted access to the PCI bus.

Arbitration on PowerSpan II is hidden. Hidden arbitration means it occurs during the previous access

so that no PCI cycles are consumed due to arbitration

—

except when the bus is in an idle state.

In the Single PCI PowerSpan II, PCI_REQ#[7:5]/PCI_GNT#[7:5] are assigned to the PCI-1

arbiter.

PCI-1

Arbiter

P1_GNT[4:1]#

P1_REQ[4:1]#

4

4

3

3

PCI-2

Arbiter

4

4

P2_GNT[4:1]#

P2_REQ[4:1]#

PCI_GNT[7:5]#

PCI_REQ[7:5]#

Assignable to

either PCI-1 or PCI-2