9. Resets, Clocks and Power-up Options

172

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

The options PWRUP_PB_ARB_EN, PWRUP_P1_ARB_EN, and PWRUP_P2_ARB_EN are used to

select between an external arbiter or a PowerSpan II arbiter for each interface.

PWRUP_PRI_PCI designates either PCI-1 or PCI-2 as being connected to the Primary PCI Interface

segment in the system (see

for more details on Primary PCI Interface

functionality).

When PWRUP_P1_R64_EN is enabled, the PowerSpan II PCI-1 interface drives P1_REQ64# during

assertion of P1_RST# to signal the presence of a 32-bit or

64-bit data path to all agents on the PCI-1 bus segment. This option must only be enabled when

PowerSpan II

is the Central Resource in the system.

The option PWRUP_BOOT enables the system designer to control boot from PCI or from the

processor bus. Whether this feature is enabled or disabled is dependent on system requirements (refer

to

for more information).

By enabling option PWRUP_BYPASS_EN, all PLLs in the design are bypassed. Typically, this option

must be disabled (PLL in use) in the system.

In the Single PCI PowerSpan II, the following power-up options are not configurable:

•

PWRUP_P2_ARB_EN

— no PCI-2 arbiter

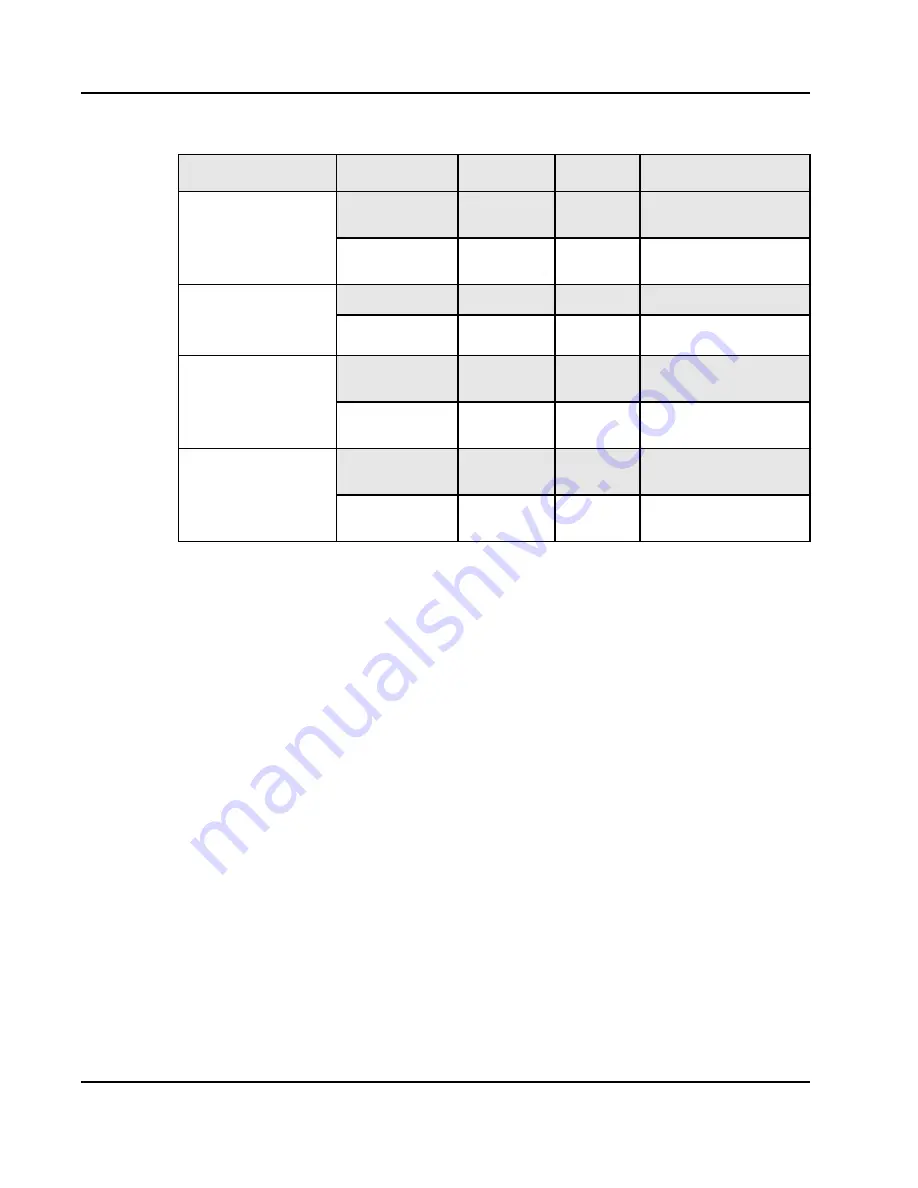

PCI-1 REQ64 Enable

(PWRUP_P1_R64_EN)

Disable

P1_REQ64_

INT[4]_=1

PB_D[4]=0

P1_R64_EN=0

Enable

P1_REQ64_

INT[4]_=0

PB_D[4]=1

P1_R64_EN=1

Boot select

(PWRUP_BOOT)

PB Boot

INT[3]_=1

PB_D[5]=0

PCI_BOOT=0

PCI Boot

INT[3]_=0

PB_D[5]=1

PCI_BOOT=1

7400 Mode Enable

(PWRUP_7400_MODE)

Disable

7400_Mode

INT[2]_=1

PB_D[6]=0

7400_MODE=0

Enable

7400_Mode

INT[2]_=0

PB_D[6]=1

7400_MODE=1

PLL Bypass Enable

(PWRUP_BYPASS_EN)

Disable PLL

Bypass

INT[1]_=1

PB_D[7]=0

BYPASS_EN=0

Enable PLL

Bypass

INT[1]_=0

PB_D[7]=1

BYPASS_EN=1

a.

The information in the System Pin column is used when PowerSpan II is in Multiplexed System Pin mode

(see

b.

The information in the PB_D Pin column is used when PowerSpan II is in Configuration Slave mode

(

Table 45: PowerSpan II Power-up Options

Power-up Option

Selection

System Pin

a

PB_D Pin

b

RST_CSR Register