11. Signals and Pinout

193

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

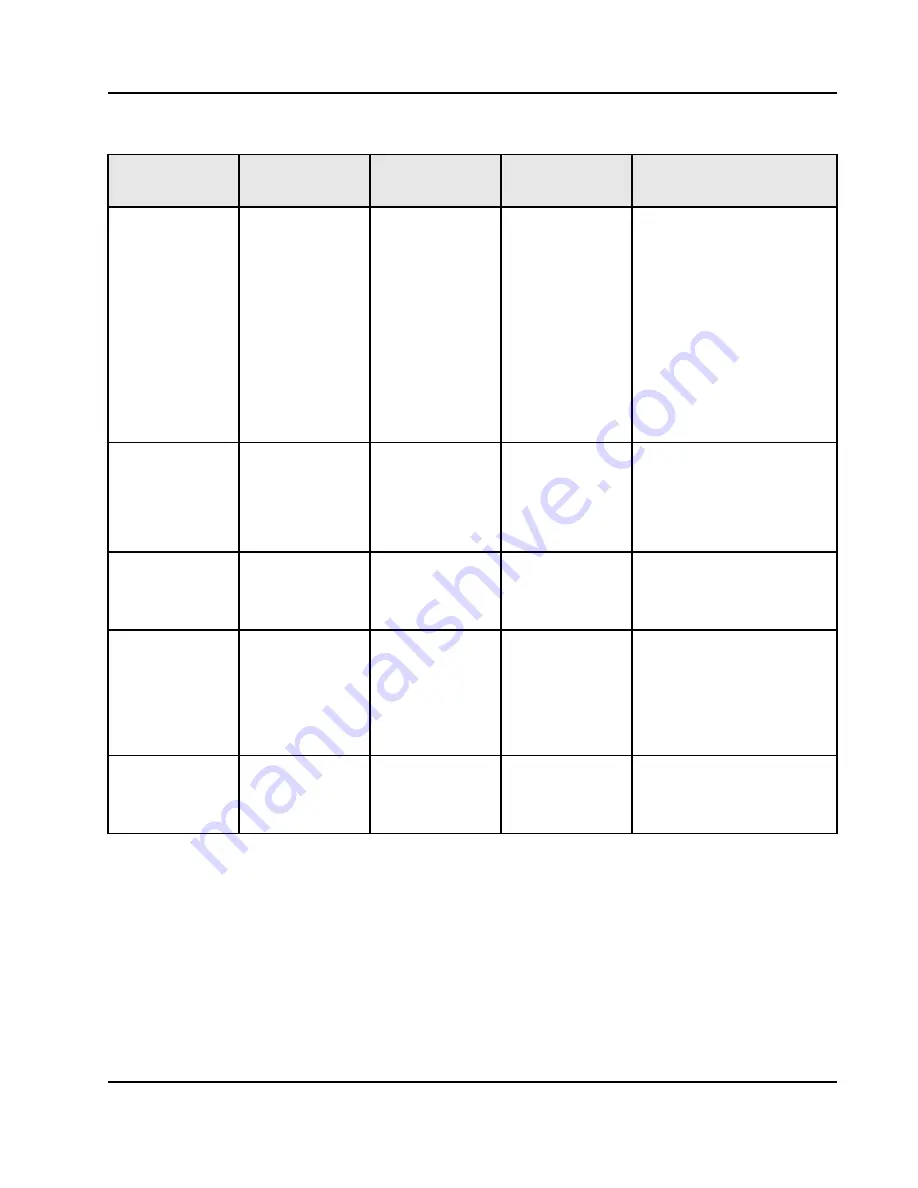

PB_BR[1]_

Tristate bidirectional

Hi-Z

Pull-up resistor

Address Bus Request:

This is

an output when an external

arbiter is used and an input when

an internal arbiter is used. As

output it indicates that

PowerSpan II requests the

ownership of the processor

address bus. As input an external

master should assert this signal

to request the ownership of the

processor address bus from

PowerSpan II’s internal arbiter.

This pin must be weakly pulled

high.

PB_BR[2:3]_

Input

Hi-Z

Pull-up resistor

Address Bus Request:

These

are inputs only. They are used by

external masters to request the

processor address bus from the

internal arbiter. These pins must

be weakly pulled high.

PB_CI_

Tristate output

Hi-Z

Pull-up resistor

Cache Inhibit:

It is used for L2

cache control. It indicates

whether the transaction should be

cached or not.

PB_CLK

Input

-

-

Processor Bus Clock:

All

devices intended to interface with

the bus processor side of the

PowerSpan II must be

synchronized to this clock. The

PB_CLK can operate up to 100

MHz.

PB_DBB_

Tristate output

Hi-Z

Pull-up resistor

Data Bus Busy:

Indicates the

ownership of the data bus. The

master who owns the processor

data bus asserts this signal.

Table 55: Processor Bus Signals

Pin Name

Pin Type

Reset State

Recommended

Termination

Description