11. Signals and Pinout

204

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

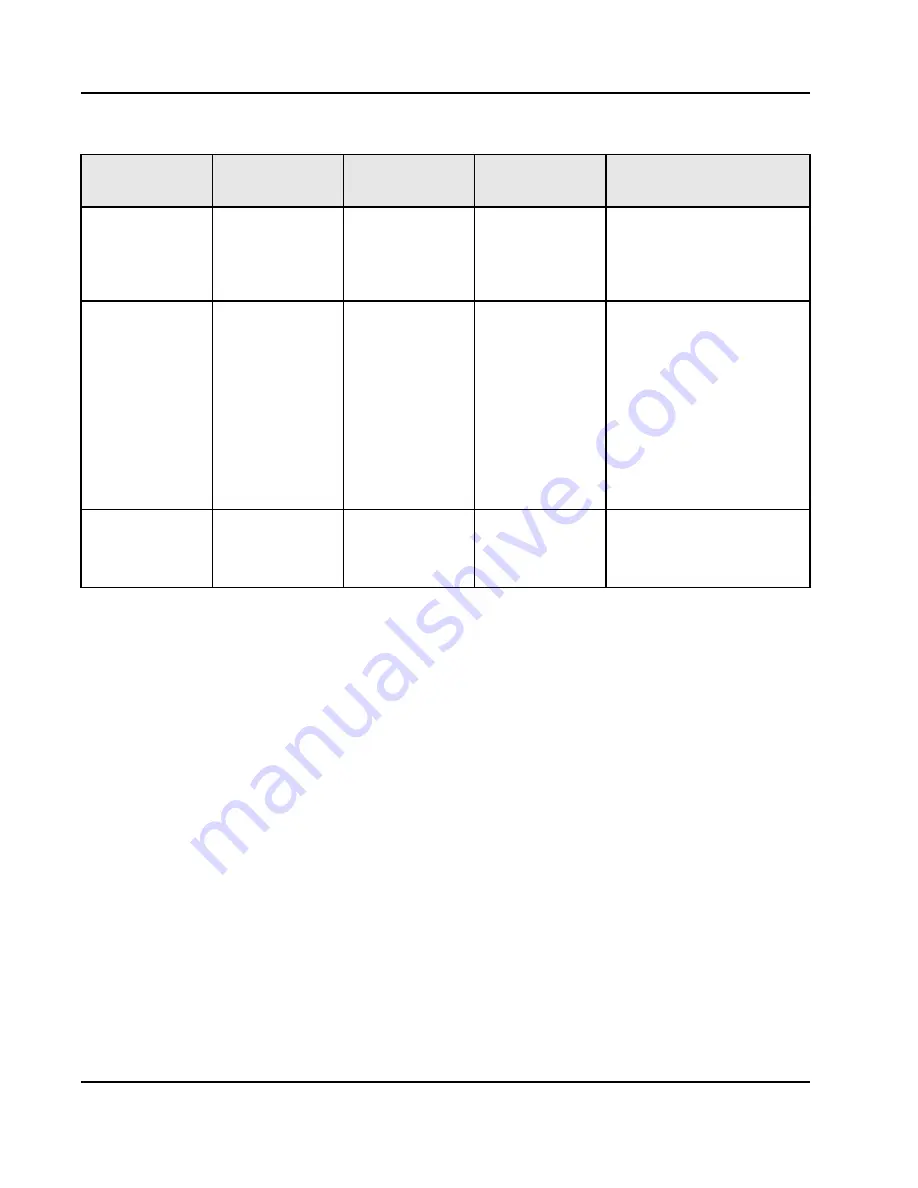

TDO

Tristate output

(LVTTL)

Hi-Z

-

Test Data Output (JTAG):

Used

(in conjunction with TCK) to shift

data and instructions into the Test

Access Port (TAP) in a serial bit

stream.

TRST_

Input

(LVTTL)

(Schmitt trigger)

Internal pull-up

resistor

Pull-down resistor if

JTAG is not used in

the system.

Otherwise the signal

must be toggled with

the PO_RST_

signal.

Test Reset (JTAG):

Asynchronous reset for the JTAG

controller. This pin must be

asserted during the power-up

reset sequence to ensure that the

Boundary Scan Register

elements are configured for

normal system operation.

Customers must assert TRST

_concurrently with PO_RST_ as

part of the power-up reset

sequence.

TE

Input

Internal pull-down

resistor

Pull-down resistor

Test Enable:

Enables

manufacturing test. IDT

recommends that system

designers pull this signal low.

Table 59: Test Signals

Pin Name

Pin Type

Reset State

Recommended

Termination

Description