12. Register Descriptions

236

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

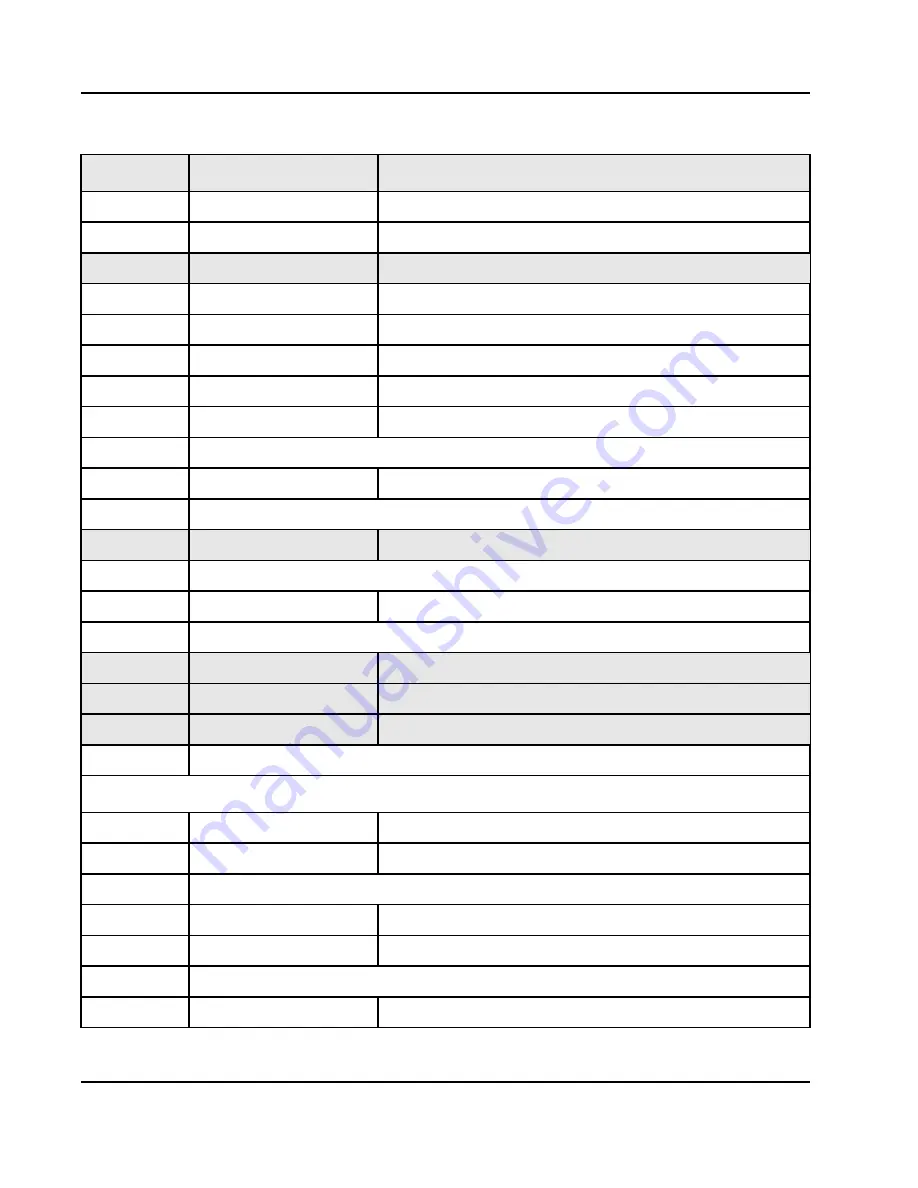

0x008

P1_CLASS

“PCI-1 Class Register” on page 254

0x00C

P1_MISC0

“PCI-1 Miscellaneous 0 Register” on page 255

0x010

P1_BSI2O

“PCI-1 I2O Target Image Base Address Register” on page 257

0x014

P1_BSREG

“PCI-1 Register Image Base Address Register” on page 258

0x018

P1_BST0

“PCI Target Base Address Register” on page 259

0x01C

P1_BST1

“PCI Target Base Address Register” on page 259

0x020

P1_BST2

“PCI Target Base Address Register” on page 259

0x024

P1_BST3

“PCI Target Base Address Register” on page 259

0x028

PCI Unimplemented

0x02C

P1_SID

“PCI System ID Register” on page 260

0x030

PCI Unimplemented

0x034

P1_CAP

“PCI-1 Capability Pointer Register” on page 261

0x038

PCI Unimplemented

0x03C

P1_MISC1

“PCI-1 Miscellaneous 1 Register” on page 262

0x040- 0x0E0

PCI Unimplemented

0x0E4

P1_HS_CSR

“PCI-1 Compact PCI Hot Swap Control and Status Register” on page 264

0x0E8

P1_VPDC

“PCI-1 Vital Product Data Capability Register” on page 266

0x0EC

P1_VPDD

“PCI-1 Vital Product Data Register” on page 267

0x0F0-0x0FC

PCI Unimplemented

PCI-1 Registers

0x100

P1_TI0_CTL

“PCI-1 Target Image x Control Register” on page 268

0x104

P1_TI0_TADDR

“PCI-1 Target Image x Translation Address Register” on page 274

0x108-0x10C

PowerSpan II Reserved

0x110

P1_TI1_CTL

“PCI-1 Target Image x Control Register” on page 268

0x114

P1_TI1_TADDR

“PCI-1 Target Image x Translation Address Register” on page 274

0x118-0x11C

PowerSpan II Reserved

0x120

P1_TI2_CTL

“PCI-1 Target Image x Control Register” on page 268

Table 64: PowerSpan II Register Map

Offset

Register Mnemonic

See