12. Register Descriptions

252

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

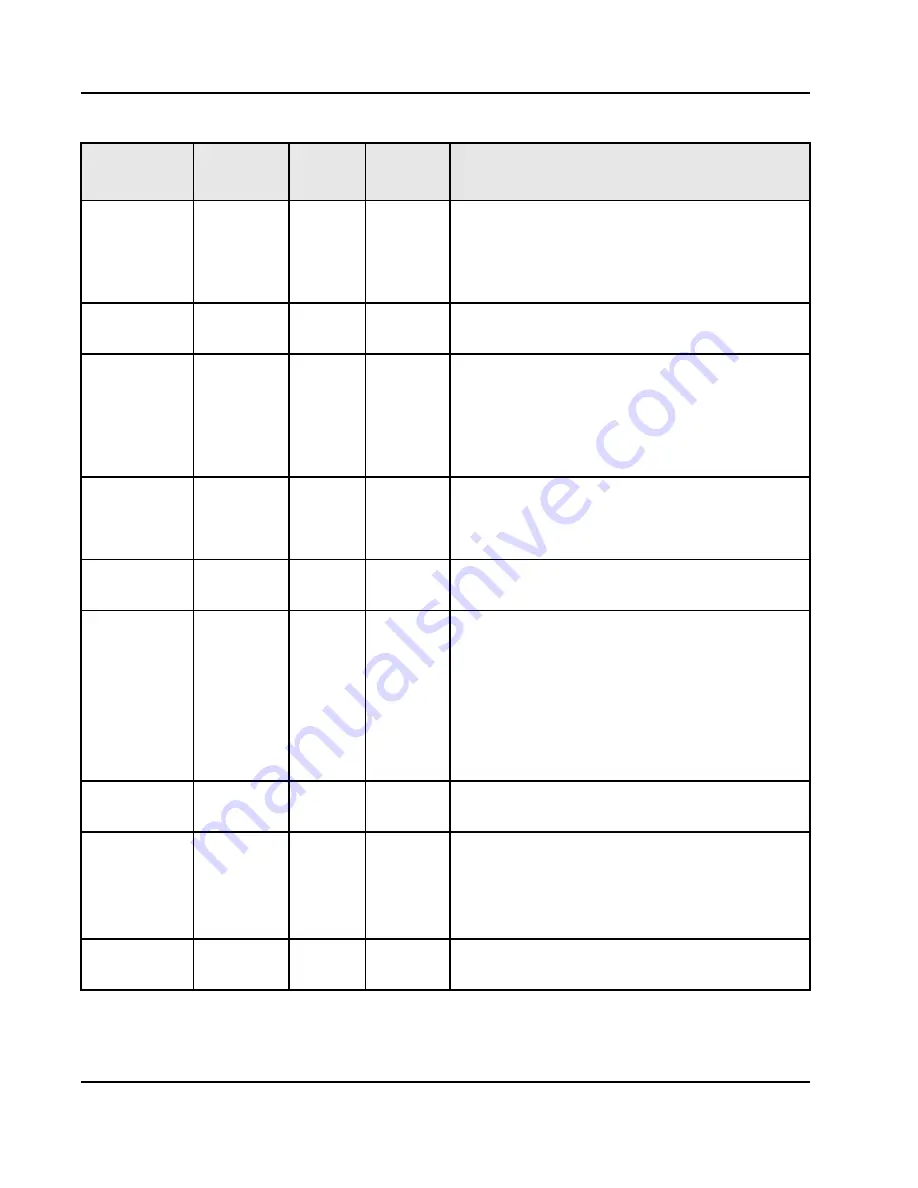

S_TA

R/W 1 to clear

P1_RST

0

Signaled Target-Abort

0 = device Target Module did not terminate transaction with

Target-Abort

1 = device Target Module terminated transaction with

Target-Abort.

DEVSEL [1:0]

R

P1_RST

01

Device Select Timing

The device is a medium speed device.

MDP_D

R/W 1 to clear

P1_RST

0

Master Data Parity Detected

The device sets this bit if the PERESP bit is set and either (a)

it is the master of the transaction in which it asserts PERR#,

or (b) the addressed target asserts PERR#.

0 = Master Module did not detect/generate data parity error

1 = Master Module detected/generated data parity error

TFBBC

R

P1_RST

0

Target Fast Back to Back Capable

Warning:

PowerSpan II cannot accept fast back-to-back

transactions - neither as the same agent nor as a different

agent.

DEV66

R

P1_RST

1

Device 66 MHz

The device is a 66 MHz capable device

CAP_L

R

P1_RST

PWRUP

Capabilities List

The capabilities list is only supported by the Primary PCI

Interface. When PCI-1 is the Primary Interface, CAP_L in

PCI-1 is set and CAP_L in PCI-2 is cleared. The opposite is

true when PCI-2 is the Primary Interface. The Primary PCI

Interface is determined by the PWRUP_PRI_PCI power-up

option.

0 = capabilities list unsupported

1 = capabilities list supported

MFBBC

R

P1_RST

0

Master Fast Back to Back Enable

The device does not generate fast back to back transactions

SERR_EN

R/W

P1_RST

0

SERR# Enable

Setting this and PERESP allows the device to report address

parity errors with SERR# as PCI target.

0 = Disable SERR# driver

1 = Enable SERR# driver

WAIT

R

P1_RST

0

Wait Cycle Control

0 = No address/data stepping

Name

Type

Reset

By

Reset

State

Function