12. Register Descriptions

253

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

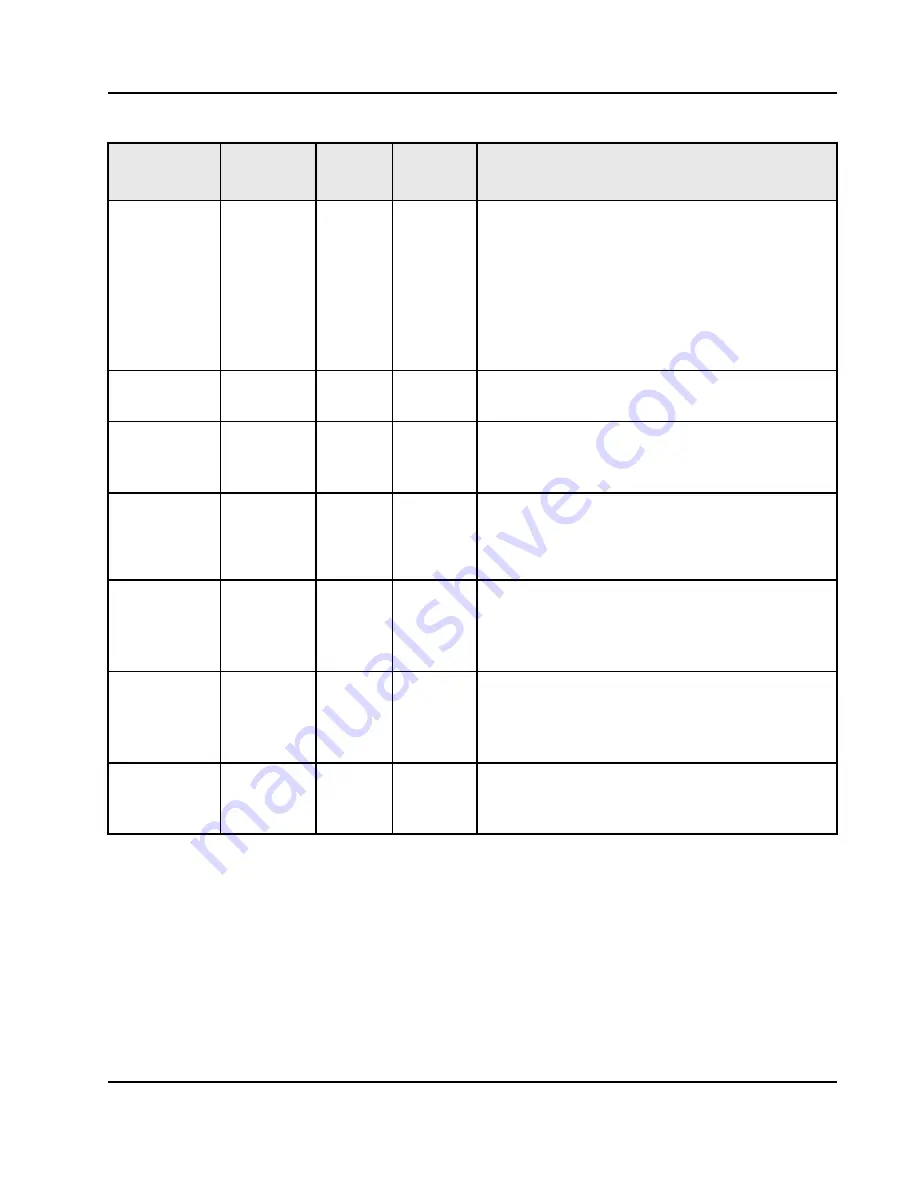

PERESP

R/W

P1_RST

0

Parity Error Response

Controls the device’s response to address and data parity

errors. When enabled, PERR# is asserted and the MDP_D

bit is set in response to data parity errors. When this bit and

SERR_EN are set, the device reports address parity errors

on SERR#. This bit does not affect the device’s parity

generation.

0 = Disable

1 = Enable

VGAPS

R

P1_RST

0

VGA Palette Snoop

0 = Disable

MWI_EN

R

P1_RST

0

Memory Write and Invalidate Enable

PowerSpan II does not generate MWI transactions.

0 = Disable

SC

R

P1_RST

0

Special Cycles

PowerSpan II does not respond to Special cycles as a PCI

target.

0 = Disable

BM

R/W

P1_RST

0

EEPROM

Bus Master

Enables the device to generate cycles as a PCI Master.

0 = Disable

1 = Enable

MS

R/W

P1_RST

0

EEPROM

Enables the device to accept Memory cycles as a PCI target.

Memory Space

0 = Disable

1 = Enable

IOS

R

P1_RST

0

IO Space

PowerSpan II does not respond to I/O cycles as a PCI target.

0 = Disable

Name

Type

Reset

By

Reset

State

Function