1. Functional Overview

29

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

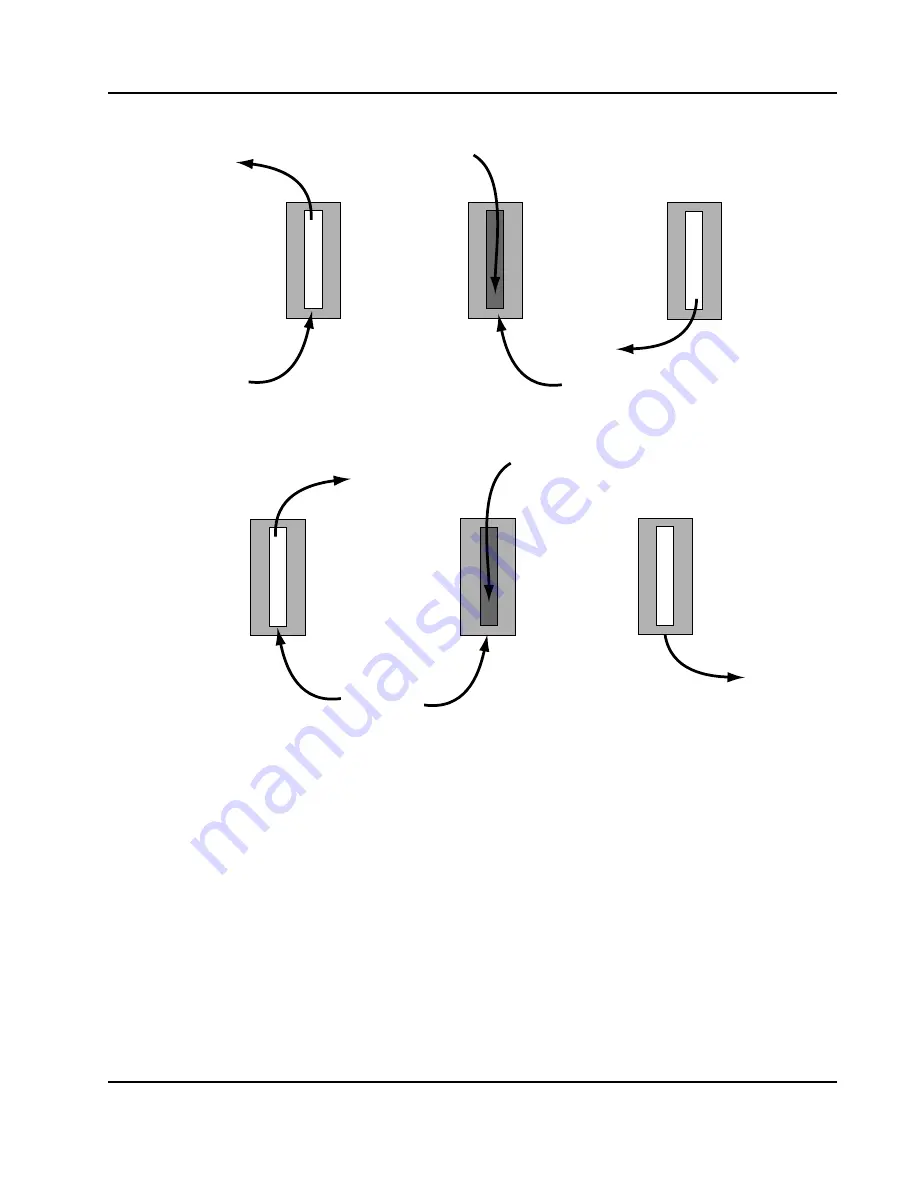

Figure 5: Reads with Conventional FIFO-Based Bridges

When Master 2 is retried in Step 2, no information is latched about the read request. When Master 2

returns for a subsequent read request in Step 4, it is treated by the bridge as the first read request.

1.6.2

PowerSpan II’s Concurrent Read Applications

1.6.2.1

PCI Host Bridge

In a PCI host bridge application, all of the PCI masters

—

for example, I/O controllers

—

potentially

receive only one retry before receiving read data. Even with another read pending, when the PCI Target

Interface of the PCI host device receives a read request, it latches the information and begins another

burst read prefetch on the processor bus. The PCI host bridge latches the addresses and delivers the

data to each master using separate, dedicated buffering. This approach greatly reduces the overall

system latency and allows for a more scalable I/O subsystem.

Master 1: Makes a

read request.

READ 1 Request

1.

Master 1: Takes the read data.

2.

READ 2 Request

Master 2: Makes a read

request and is retried.

Master 2: Makes another

read request.

4.

READ 2

READ 1

Master 1: Makes another

request and is retried.

3.

Master 2: Takes the read data.

6.

5.