12. Register Descriptions

294

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.25

Processor Bus Slave Image x Base Address Register

This register defines the lowest address of the slave image. The minimum image size is 4 Kbyte as

defined in BS field in the PB_SIx_CTL.

The initial write to this register sets the IMG_EN bit in the

“Processor Bus Slave Image x Control

. Subsequent writes to this register will have no effect on the IMG_EN bit.

A base address of 0 is valid.

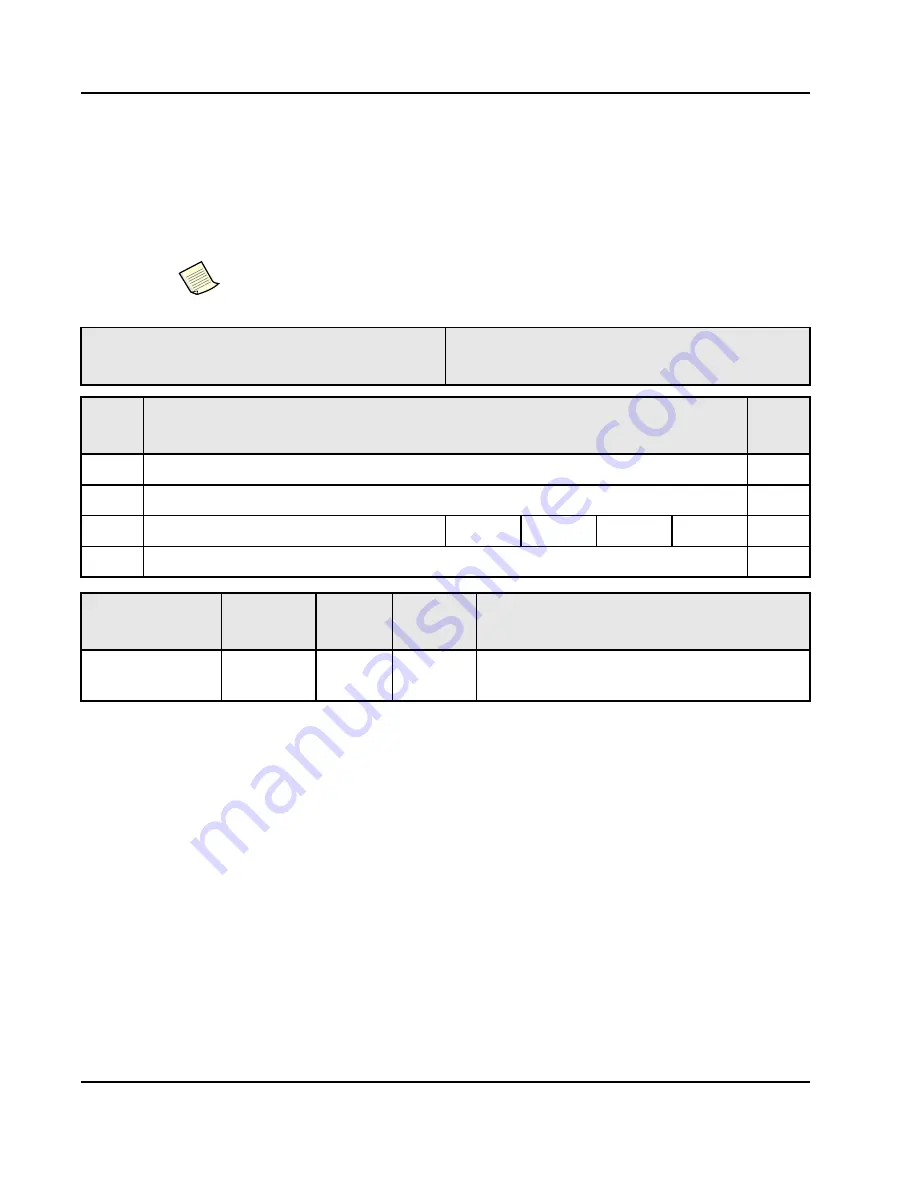

Register Name: PB_SIx_BADDR

Register Offset: 0x208, 0x218, 0x228, 0x238, 0x248,0x

258, 0x268, 0x278

PCI

Bits

Function

PB

Bits

31-24

BA

0-7

23-16

BA

8-15

15-08

BA

0

0

0

0

16-23

07-00

PowerSpan II Reserved

24-31

Name

Type

Reset

By

Reset

State

Function

BA[19:0]

R/W

PB_RST

0 EEPROM

Processor Bus Base Address