12. Register Descriptions

310

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.36

DMA x Destination Address Register

This register specifies the starting byte address on the destination port for channel DMAx. This register

is programmed for a Direct mode DMA or programmed by the Linked-list when loading the command

packet.

The DMAx_DST_ADDR register is updated during the DMA transaction. Writing to this register

while the DMA is active has no effect. While the DMA is active, this register provides status

information on the progress of the transfer.

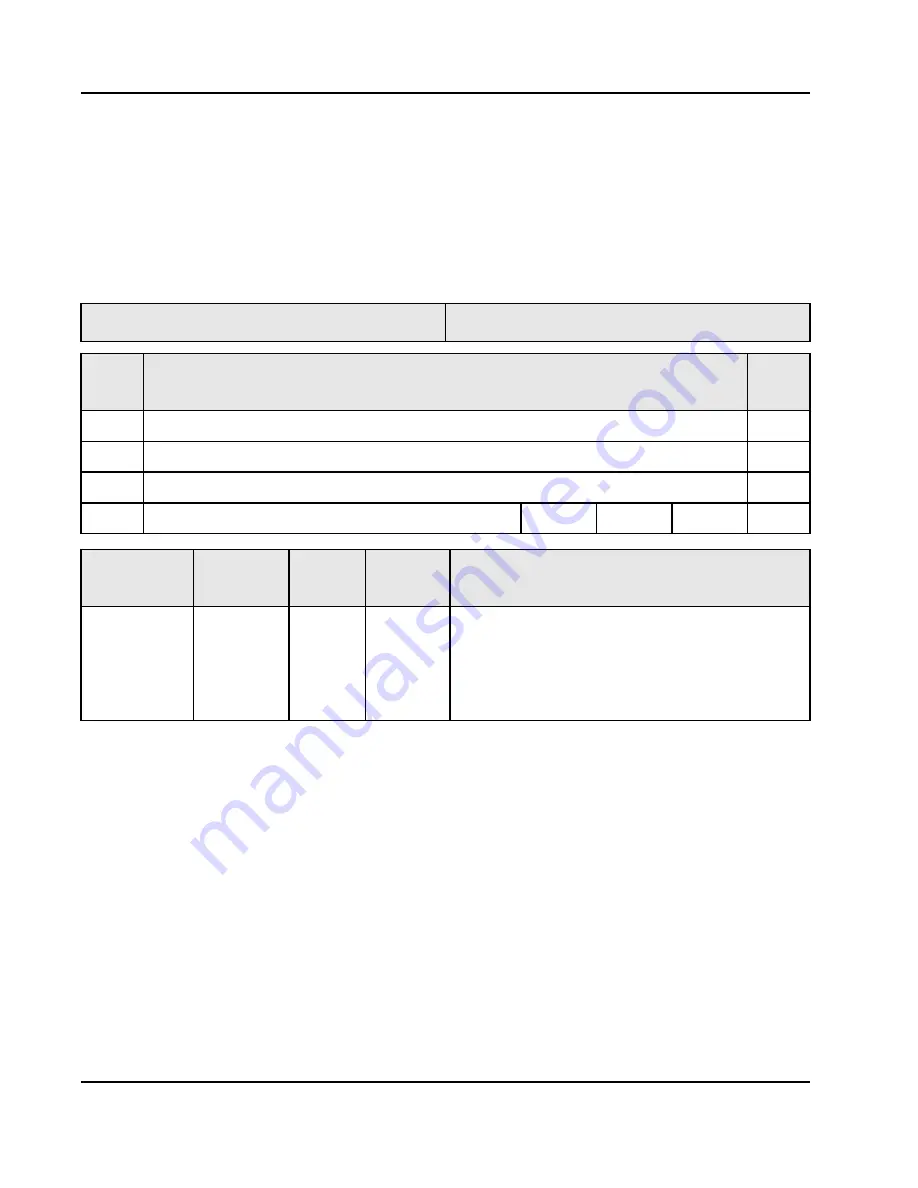

Register Name: DMAx_DST_ADDR

Register Offset: 0x30C, 0x33C, 0x36C, 0x39C

PCI

Bits

Function

PB

Bits

31-24

DADDR

0-7

23-16

DADDR

8-15

15-08

DADDR

16-23

07-00

DADDR

0

0

0

24-31

Name

Type

Reset

By

Reset

State

Function

DADDR[31:3]

R/W

G_RST

0

Starting byte address on the destination bus for the port

defined by DST_PORT field in the

.

The lower three bits of the destination address is identical to

the lower three bits of the source address

(DMAx_SRC_ADDR)