12. Register Descriptions

313

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

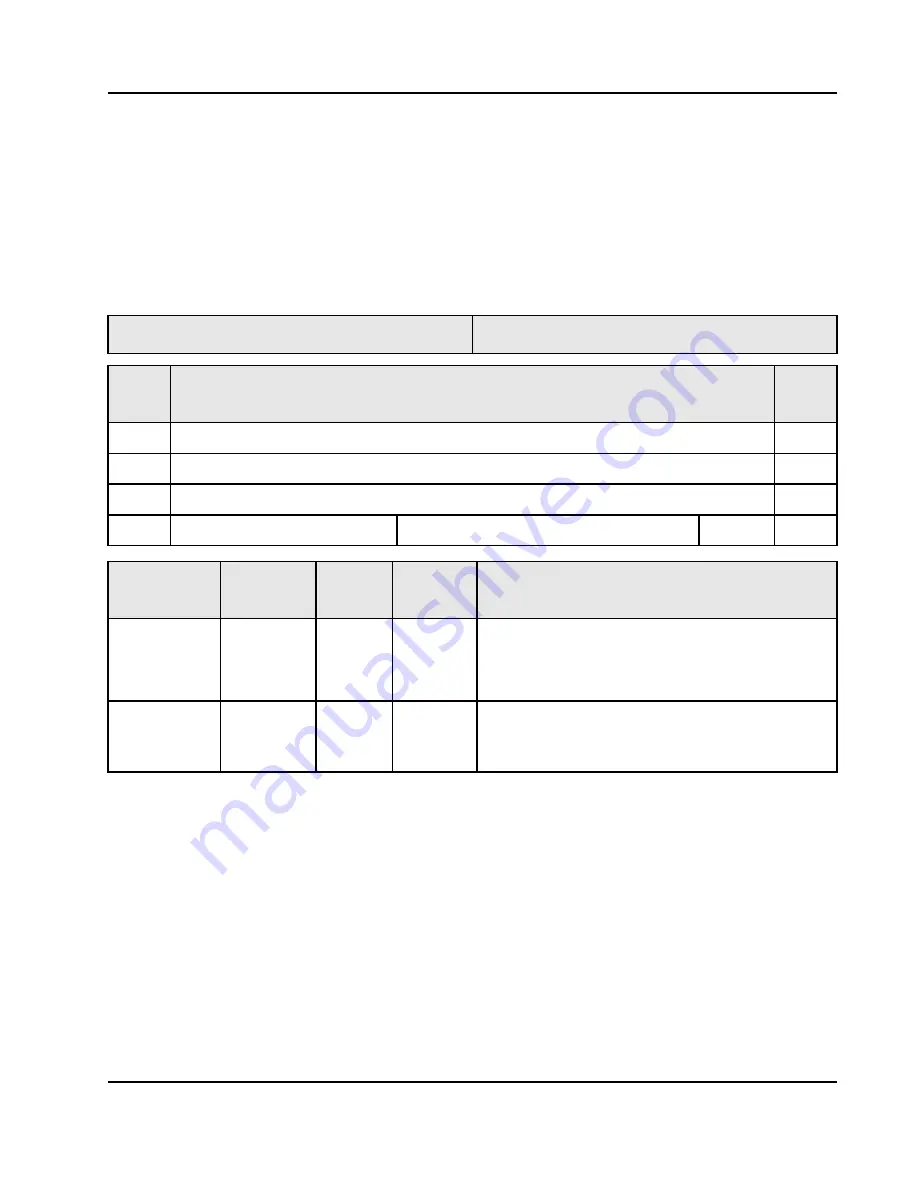

12.5.38

DMA x Command Packet Pointer Register

This register specifies the 32-byte aligned address of the next command packet in the Linked-List for

channel DMAx. It is programmed by PowerSpan II from the Linked-list when loading the command

packet.

The DMAx_CPP register is updated at the start of a Linked-list transfer and remains constant

throughout the transfer. Writing to this register while the DMA is active has no effect.

For a Direct mode DMA transfer, this register does not need to be programmed.

Register Name: DMAx_CPP

Register Offset: 0x31C, 0x34C, 0x37C, 0x3AC

PCI

Bits

Function

PB

Bits

31-24

NCP

0-7

23-16

NCP

8-15

15-08

NCP

16-23

07-00

NCP

PowerSpan II Reserved

LAST

24-31

Name

Type

Reset

By

Reset

State

Function

NCP[31:5]

R/W

G_RST

0

Next Command Packet Address.

Points to a 32-byte aligned memory location of a linked-list on

the port specified by the CP_PORT bit in the DMAx_ATTR

register.

LAST

R/W

G_RST

0

Last Item

0 = more items in linked list

1 = last item in linked list