12. Register Descriptions

315

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

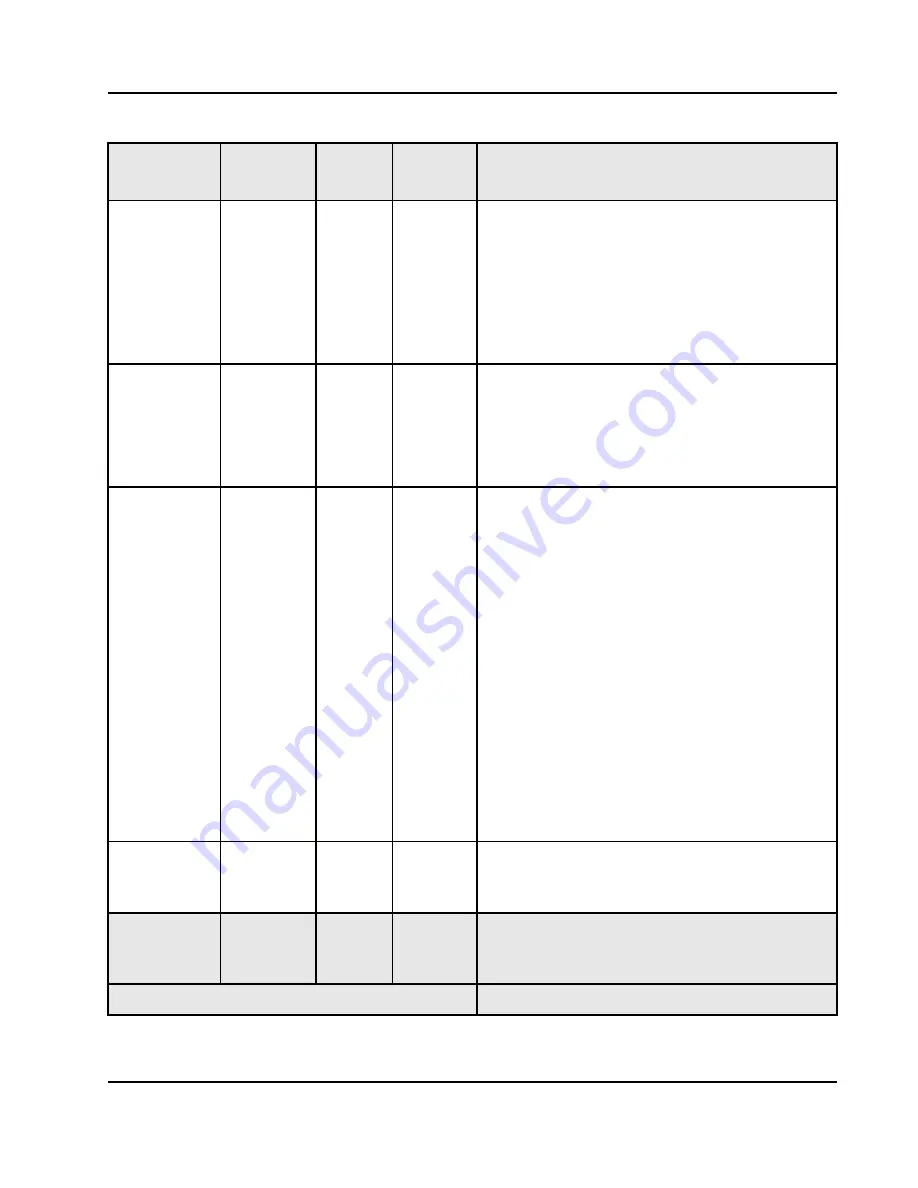

DBS[1:0]

R/W

G_RST

0

DMA Block Size (when DBS_EN is set to 1)

Controls the byte size of transactions generated by the DMA

channel. The DBS_EN bit must be set to 1 in order for the

DBS functionality to be enabled.

00=32 bytes

01=16 bytes

10=8 bytes

11=4 bytes

DBS_EN

R/W

G_RST

0

DMA Block Size Enable

Provides programmable control over the byte size of

transactions generated by the DMA channel. The byte size is

based on values programmed into DBS[1:0].

0 = not active

1 = active

OFF

R/W

G_RST

0

DMA Channel Off Counter (number of PB clocks)

Provides programmable control over the amount of source

bus traffic generated by the DMA channel. The channel will

interleave source bus transfers with a period of idle

Processor Bus clocks where no source bus requests are

generated. When source and destination ports are different,

256 bytes of source bus traffic occur before the idle period. If

source and destination ports are the same, 64 bytes of

source bus traffic occur before the idle period. This helps

prevent PowerSpan II from interfering with Processor Bus

instruction fetches.

000 = 0

001 = 128

010 = 256

011 = 512

100 = 1024

101 = 2048

110 = 4096

111 = 8192

P1_ERR

R/Write 1 to

Clear

G_RST

0

PCI-1 Bus Error

0 = no error

1 = error

P2_ERR

R/Write 1 to

Clear

G_RST

0

PCI-2 Bus Error

0 = no error

1 = error

Single PCI PowerSpan II: Reserved

Name

Type

Reset

By

Reset

State

Function