12. Register Descriptions

352

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.62

PCI I2O Target Image Control Register

This register contains the control information for the PowerSpan II PCI I

2

O Target Image. The lower

4 Kbytes of the image provide the I

2

O Shell Interface - Inbound and Outbound Queues and the Host

Interrupt Status and Mask Registers. I

2

O Message Frames are accessible above the 4-KByte boundary.

The Queues and the Message Frames reside in memory connected to the processor bus.

All PCI transactions claimed by the image are destined for the Processor Bus

The following parameters do not affect Processor Bus transactions generated by I

2

O Shell accesses:

•

TA_EN: no address translation for I

2

O Shell accesses

•

PRKEEP: no read keep for I

2

O Shell accesses

•

END

•

RD_AMT: prefetch amount fixed at 8 bytes for I

2

O Shell accesses.

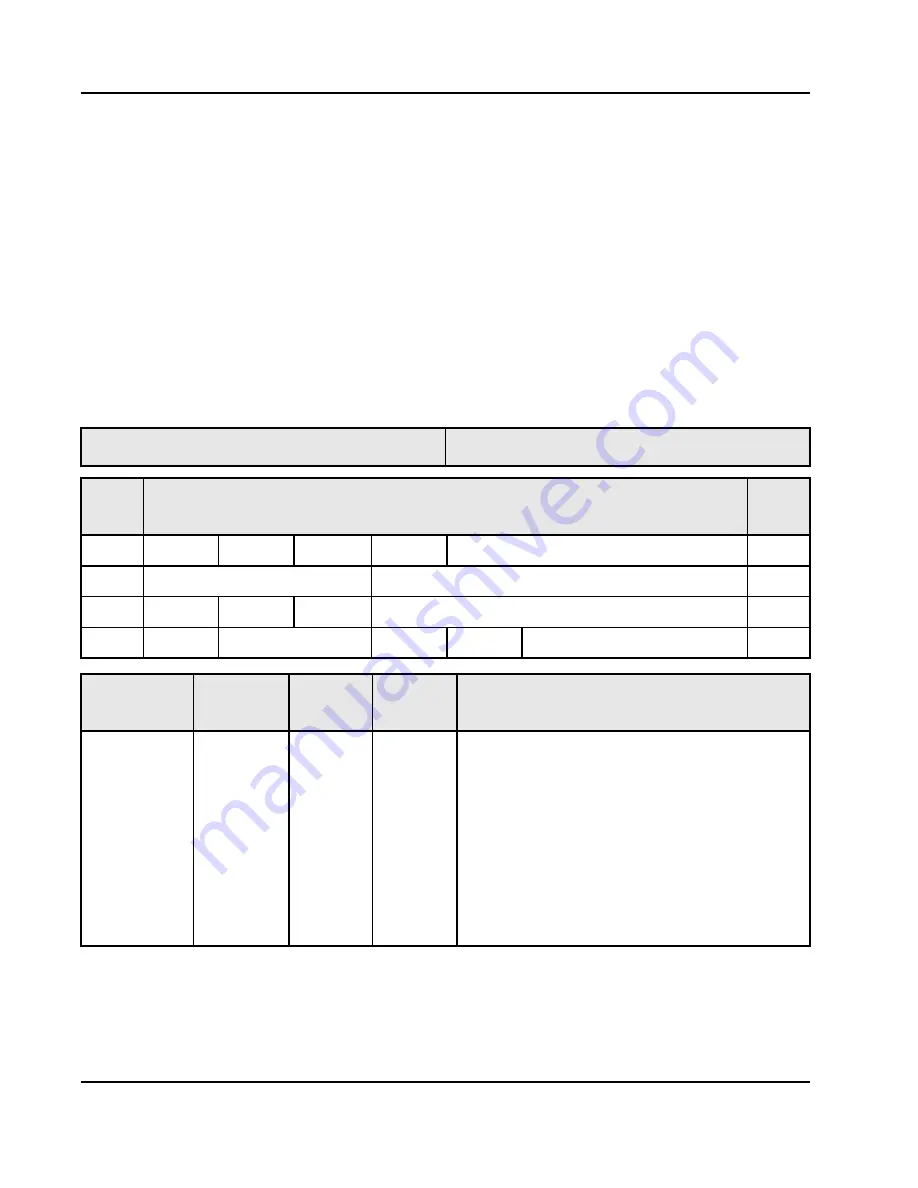

Register Name: PCI_TI2O_CTL

Register Offset: 0x500

PCI

Bits

Function

PB

Bits

31-24

IMG_EN

TA_EN

BAR_EN

0

BS

0-7

23-16

PowerSpan II Reserved

RTT

8-15

15-08

GBL

CI

0

WTT

16-23

07-00

PRKEEP

END

MRA

0

RD_AMT

24-31

Name

Type

Reset

By

Reset

State

Function

IMG_EN

R/W

PRI_RST

0

Image Enable

The Image Enable bit can be changed with the following

actions:

• initial write to the BA field in the

Base Address Register” on page 257

• register write to IMG_EN

The image enable is cleared by writing a zero to IMG_EN or

writing zero to the BA field in the Px_BSI2O. This effectively

disables I2O functionality.

0 = Disable

1 = Enable