12. Register Descriptions

376

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.80

I2O IOP Outbound Index Register

This register is required for PowerSpan II I2O Outbound Option support. This register indicates the

address in Host memory to which the IOP is to post the next Outbound XMFA. The IOP maintains this

register.

If the I2O Host Outbound Index Register and the I2O IOP Outbound Index Register differ, then the

Outbound Post List Interrupt Status bit is set in the OPL_IS register at offset 0x30 of the PCI I2O target

Image. When these registers contain the same Host memory address, the Interrupt is cleared.

This feature is only supported when the I2O Outbound Option is enabled with the XI2O_EN bit in the

“I2O Control and Status Register” on page 357

The HOPL_SIZE bit in the

“I2O Control and Status Register” on page 357

determines the alignment of

this Index Register.

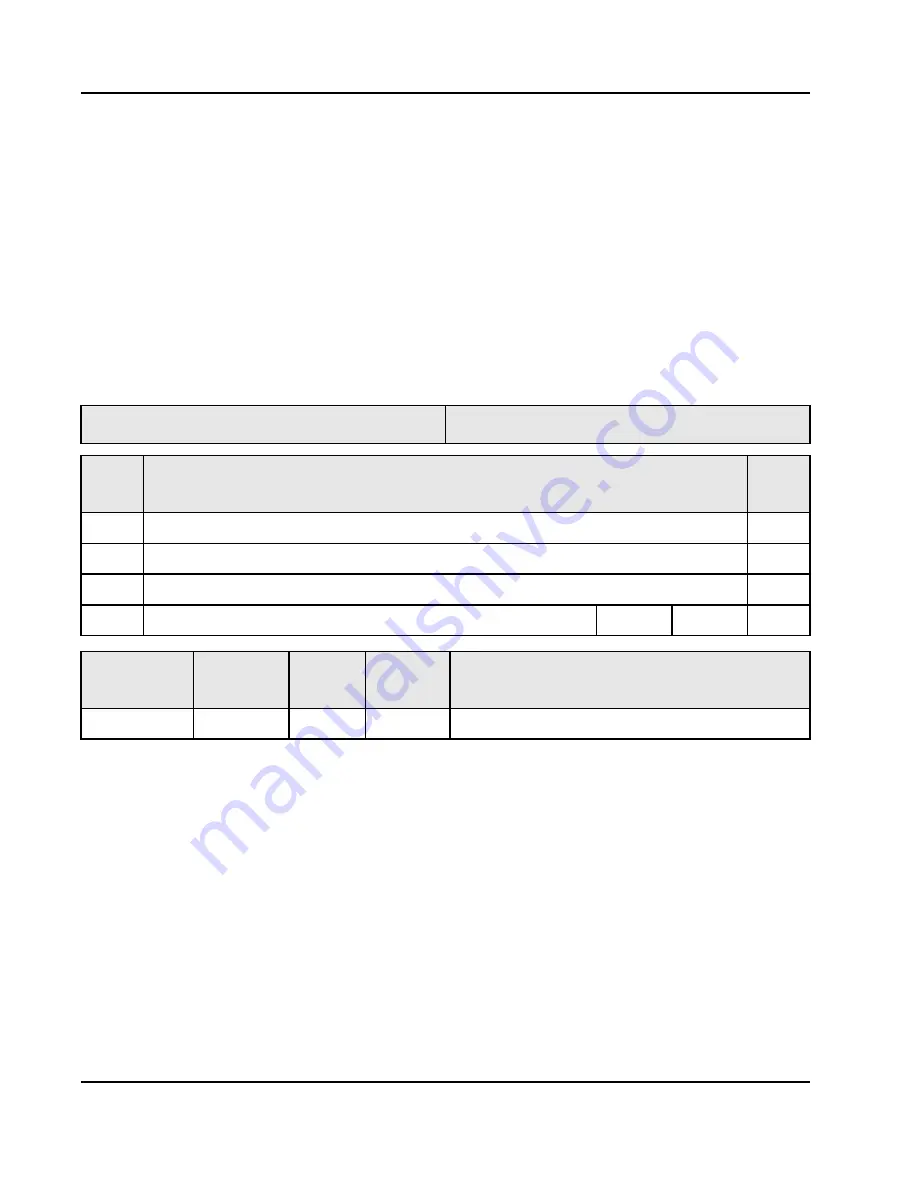

Register Name: IOP_OI

Register Offset: 0x548

PCI

Bits

Function

PB

Bits

31-24

OI

0-7

23-16

OI

8-15

15-08

OI

16-23

07-00

OI

0

0

24-31

I

Name

Type

Reset

By

Reset

State

Function

OI[29:0]

R/W

PRI_RST

0

IOP Outbound Index