B. Typical Applications

422

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

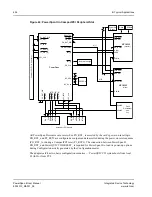

The PowerSpan II PB Interface fully supports the multi processing cache coherent aspects of the

processor bus. The PowerSpan II PB Interface can only interact with 64-bit port size agents.

The presence of the PowerPC 7xx limits the extent of extended cycle support in the system depicted in

Figure 43: PowerSpan II in Multi-processor 60x system

The SIZ[0] pin is hardwired on PowerSpan II and the PowerQUICC II. PowerSpan II must

operate with extended cycles disabled. It is still possible for the PowerQUICC II bus master

to target SDRAM with extended cycles.

PowerSpan

PB_CLK

PB_BR[3]

PB_BG[3]

PB_BG[2]

PB_BG[1]

PB_TSIZ[1:3]

PB_GBL, PB_CI

PB_AACK

PB_D[0:63], PB_DP[0:7]

PB_TA

PB_DVAL

PB_TEA

Clock Source

CLKIN

A[0:31], AP[0:3], TT[0:4], TBST

TSIZ[1:3]

ARTRY

DH[0:31], DL[0:31], DP[0:7]

BR

BG

ABB

GBL, CI

TS

AACK

APE

DBG

DBB

TA

DVAL

TEA

MPC8260

SYSCLK

A[0:31], AP[0:3], TT[0:4], TBST

DH[0:31], DL[0:31], DP[0:7]

DPE

TSIZ[0:2]

BR

BG

ABB

GBL, CI

TS

ARTRY

AACK

APE

DBG

DBB

TA

TEA

DRTRY

DBDIS

MPC740

2MX8

2MX8

A[10:0]

address latch

and m

u

x

SD

A10_GPL0

ALE

SD

AMUX_GPL5

PSD

WE_GPL1

POE_SDRAS_GPL2

PSDCAS_GPL3

CSO

WE_DQM_BS_B[0:7]

8 SDRAM

A[0:31]

PB_BR[2]

PB_BR[1]

PB_ABB

PB_DBG[3]

PB_DBG[2]

PB_DBG[1]

PB_DBB

PB_A[0:31], PB_AP[0:3], PB_TT[0:4], PB_TBST

PB_TS

PB_ARTRY

[1:3]

TLBISYNC

TSIZ[0]

PB_TSIZ[0]