B. Typical Applications

424

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

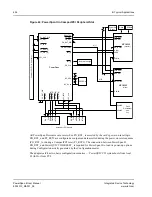

Figure 44: PowerSpan II in CompactPCI Peripheral Slot

All PowerSpan II resources are reset when PO_RST_ is asserted by the card’s power on reset logic.

PB_RST_ and P2_RST# are configured as outputs and are asserted during the power on reset sequence

(PO_RST_) or during a CompactPCI reset (P1_RST#). The connection between PowerSpan II

PB_RST_ and PowerQUICC II HRESET _is required for PowerSpan II to load its power-up options

during Configuration activity generated by the Configuration master.

The adapter card has two basic configuration scenarios

—

PowerQUICC II system boots from local

FLASH or from PCI.

P1_RST_DIR

P1_RST

P1_INTA

P1_REQ[1]

P1_GNT[1]

P1_CLK

PO_RST

PB_RST

PB_RST_DIR

INT[0]

PB_CLK

PB_RSTCONF

I2C_SDA

I2C_SCLK

EEPROM

P2_CLK

P2_INT

A

P2_GNT[2]

P2_REQ[2]

P2_GNT[1]

P2_REQ[1]

P2_RST

P2_RST_DIR

PowerSpan

Compact PCI P1/J1 Connector

RST#

CLK

REQ#

GNT#

INT

A#

RST#

CLK

REQ#

GNT#

INT

A#

Secondary PCI Agents

66MHZ

33MHZ

Clock

Generataor

and

PLL

CLKIN

RSTCONF

HRESET

PORESET

CLKIN

IRQ0

A[0:6]

RSTCONF

HRESET

PORESET

MPC8260

MPC8260

Power On

Reset

Flash

EEPROM

A[0]

A[1]

HEALTHY

Board Interrupts

INT[2]

(master)

(slave)