B. Typical Applications

425

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

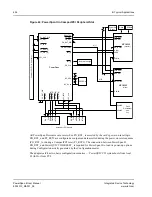

When the PowerQUICC II system boots from local FLASH there are two possible scenarios which can

occur. In the first case, after reset, PowerSpan II retries all accesses to its Primary PCI target. The

PowerQUICC II configures the PowerSpan II Primary and Secondary Base Address Registers and then

configures all agents on the Secondary bus. The PowerQUICC II then enables accesses to the

PowerSpan II Primary PCI target. The CompactPCI Host then completes the configuration of all

Primary PCI agents.

In the second scenario, an agent on the PCI secondary bus configures all agents there. The PowerSpan

II Secondary PCI target retries all accesses until the PowerQUICC II completed configuration of

PowerSpan II Secondary Base Address Registers.

B.2.3

CompactPCI Host Card

PowerSpan II supports the PowerQUICC II as a Host in a CompactPCI system. The application

illustration,

, shows a directly connected PowerSpan II in a PowerQUICC II system, which is

supported by the PowerPC 7xx.

PowerSpan II has reset and arbitration functionality for the Primary and Secondary PCI bus segments.

PB_RST_ is configured as an input while both P1_RST# and P2_RST# are outputs. A processor

power-on reset or hard reset resets both Primary and Secondary PCI bus segments.

The card provides clocks for the embedded PowerPCs, PowerSpan II’s PB Interface, all secondary PCI

agents, as well as the multiple clocks required for the CompactPCI backplane.

PowerSpan II’s bidirectional interrupt pins are used to handle all four CompactPCI interrupts and the

Hot Swap system enumeration interrupt. All interrupts are routed to the PowerPC 7xx through

PowerSpan II pin INT[5]_.

The PowerQUICC II system boots from local FLASH on the card. The PowerQUICC II uses

PowerSpan II to configure all PCI agents on the Primary and Secondary PCI buses.

PowerSpan II supports system boot from PCI with the processor bus arbiter.