438

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

STOP_REQ

STOP#

Sync Block

System Boot

T

Target-Abort

Target-Disconnect

Target-Retry

Termination Phase

PB master

PB slave

PCI master

PCI target

Test Signals

tlb invalidate

tlb sync

Transaction Length

PB master

PB slave

Transaction Mapping

PB master

PCI master

PCI target

TRDY#

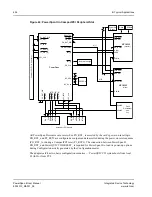

Typical Applications

V

Vital Product Data

defined

EEPROM

Primary PCI

reading

writing

VPD_EN

W

Window of Opportunity

defined

Write with Flush

Write with flush

Write with flush atomic

Write with kill

WTT[4:0]