2. PCI Interface

61

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

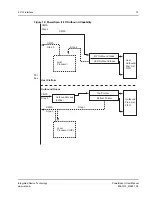

During a read access, the VPD Address (VPDA) field and the VPD Flag (F) bit are written in the

“PCI-1 Vital Product Data Register” on page 267

. The F bit must be set to 0 to indicate a VPD read

access. PowerSpan II sets the F bit to 1 when it completes reading the 4 bytes from the EEPROM. The

F bit must be polled to determine when the read is complete. Byte 0 (bits 7 through 0) of the

Vital Product Data Register” on page 267

contains the data referenced by the VPD Address

—

bytes 1

through 3 contain the successive bytes.

2.5.3

Writing VPD Data

A write can only occur to the upper 128 bytes of the EEPROM or, potentially, the upper 192 bytes if

I

2

C chip select is non-zero. Similar to the read operation, the write operation always writes four

consecutive bytes starting from the VPD address to the EEPROM.

“PCI-1 Vital Product Data Register” on page 267

is written with the 4 bytes of data. Byte 0

(register bits 7 - 0) contains the data to be written to the location referenced by the VPD Address. Bytes

1-3 contain the data for the successive bytes. The VPDA field and the F bit is then written. The F bit

must be set to 1 to indicate a VPD write. The F bit is polled to determine when the write to the

EEPROM is completed. PowerSpan II sets the F bit to 0 when the write is completed.

When a write is attempted to the lower 64 bytes of the VPD area of the EEPROM, PowerSpan II does

not perform the write operation and clears the F bit.

If the Px_VPDD register or the I2C_CSR register is written to prior to the flag bit being set to

1, the results of the original read operation are unpredictable.

The Px_VPDD or I2C_CSR register must not be written while a write operation is occurring.