2. PCI Interface

74

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

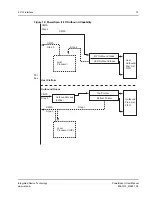

PowerSpan II compares the value of the Host Outbound Index Register to the IOP Outbound Index

Register. If they are identical the Interrupt is cleared by the PowerSpan II. If these registers differ, then

it is assumed that the PowerSpan II has posted additional Outbound reply messages which have not yet

been serviced by the Host, and therefore, the PowerSpan II continues to assert the Interrupt to the Host.

The Host will post empty MFAs back to the IOP by writing to the PowerSpan II’s Outbound Queue

Register (0x044), with the C bit set to zero. PowerSpan II services the written MFA the same as a

normal Outbound MFA being returned to the IOP.

illustrates the following steps in PowerSpan II I

2

0 outbound capability:

1.

Local processor reads the Outbound Free List to obtain an MFA

2.

Local processor writes the MF in the Host memory

3.

Local processor writes the MFA to the Host Outbound Post List FIFO, setting the P bit

4.

Host processor reads the XMFAs from the Host Outbound Post List

5.

Host writes the XMFA to the Outbound Queue (0x044)