3. Processor Bus Interface

104

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

3.4.2.2

Transaction Length

The PB Master can generate a super-set of the data transfer sizes supported by the embedded PowerPC

family. The user can disable certain data transfer sizes that are unique to the PowerQUICC II. All data

transfer sizes supported by the PowerSpan II PB master are illustrated in

below. Burst

transfers are indicated by the assertion of Processor Bus Transfer Burst (PB_TBST_, see

). PB_TBST_ is negated during single cycle transactions (see

below).

The shaded regions in

indicate transaction sizes that are unique to the PowerQUICC II. The

extended cycles supported by the PowerQUICC II are identified with an additional size pin, Processor

Bus Transfer Size (PB_TSIZ[0]). Extended cycles are enabled using the EXTCYC bit in the

Bus Miscellaneous Control and Status Register” on page 304

The following figures,

, illustrate burst reads and burst writes on the PB

Master.

PowerSpan II only interfaces to 64-bit slaves.

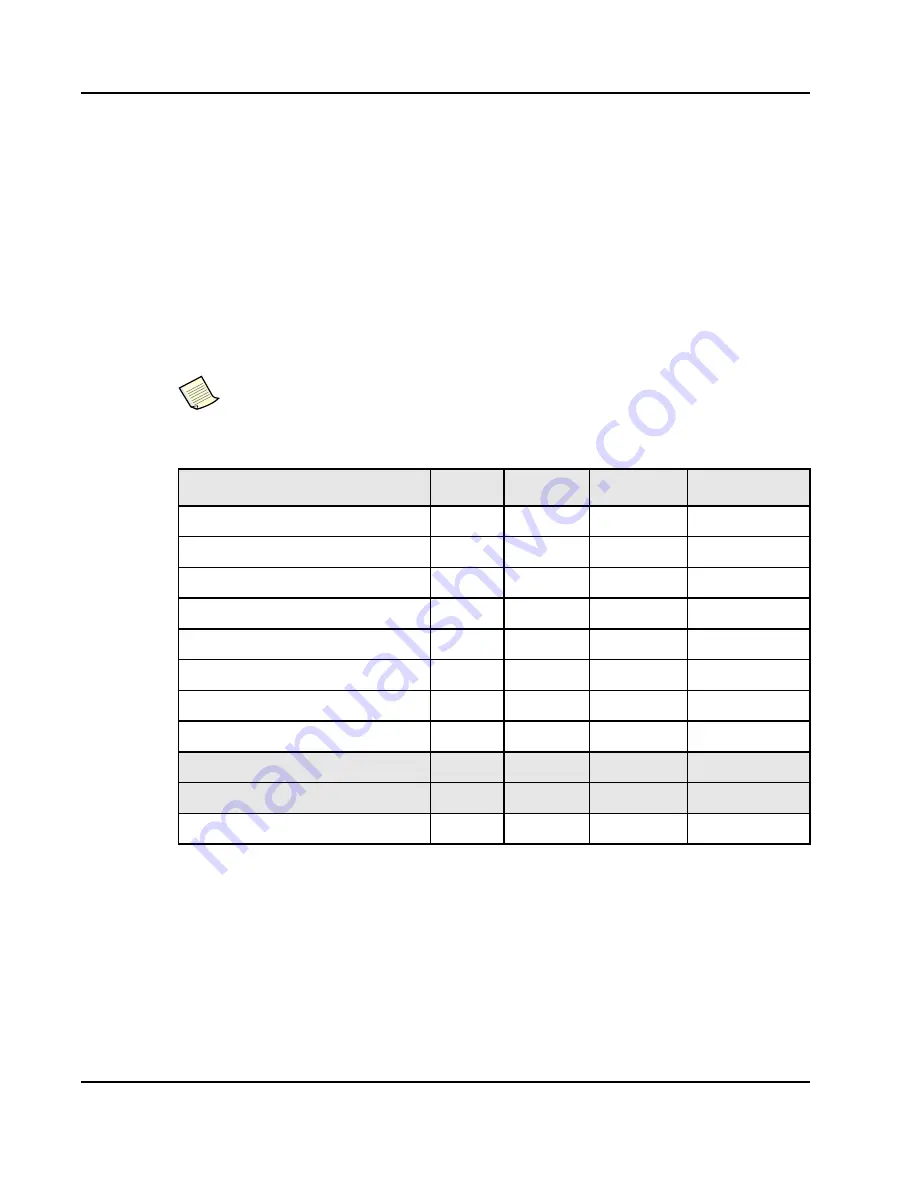

Table 22: PowerSpan II PB Transfer Sizes

Transfer Size

Bytes

PB_TBST

PB_TSIZ[0]

PB_TSIZ[1:3]

Byte

1

1

0

001

Half-word

2

1

0

010

Tri-byte

3

1

0

011

Word

4

1

0

100

Five bytes

5

1

0

101

Six bytes

6

1

0

110

Seven bytes

7

1

0

111

Double Word (DW)

8

1

0

000

Extended Double (PowerQUICC II only)

16

1

1

001

Extended Triple (PowerQUICC II only)

24

1

1

010

Burst (Quad DW)

32

0

0

010