3. Processor Bus Interface

108

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

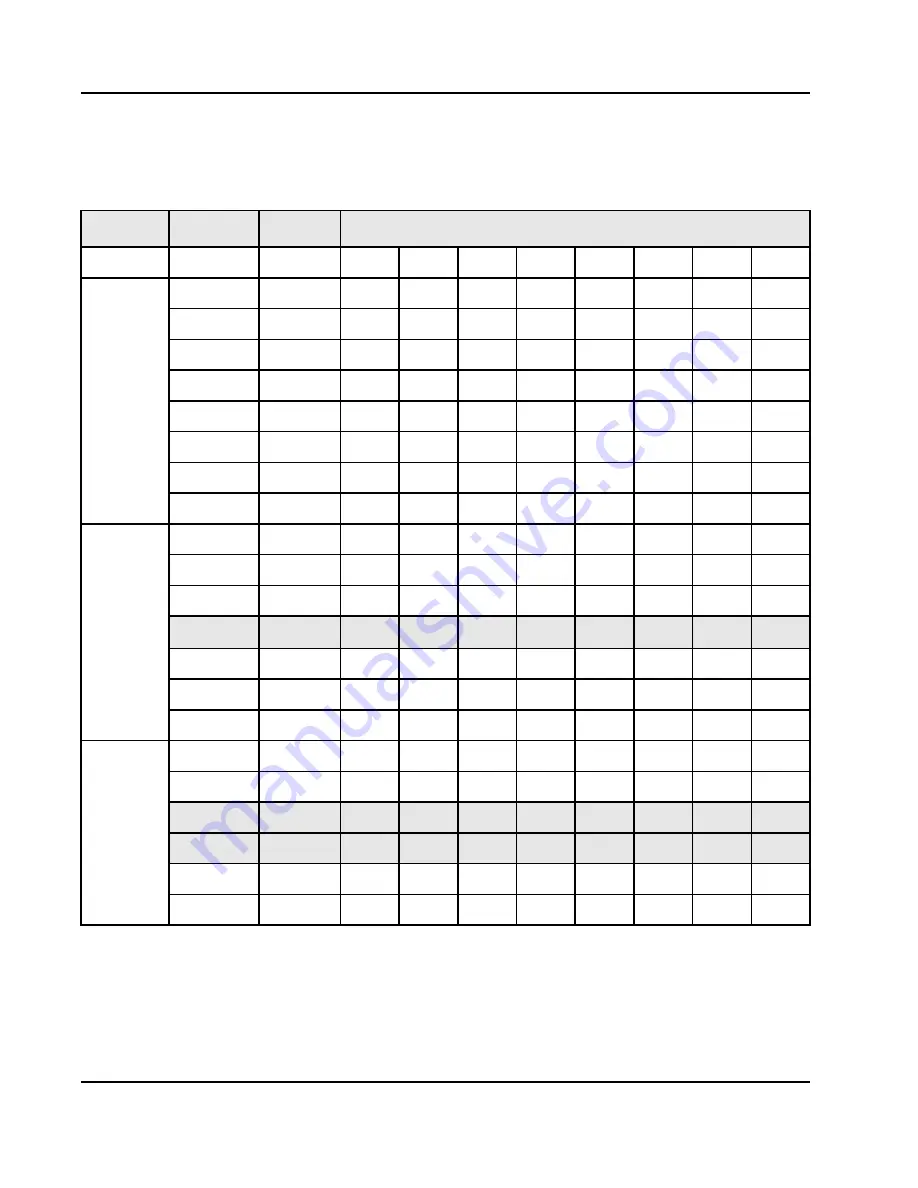

lists the size and alignment transactions less than or equal to 8-bytes. The shaded table cells

show transactions that support the

PowerPC 7400

processor.

Table 24: PowerSpan II Processor Bus Single Beat Data Transfers

Size

TSIZ[0:3]

A[29:31]

Data Bus Byte Lanes

0

1

2

3

4

5

6

7

Byte

0001

000

D0

0001

001

D1

0001

010

D2

0001

011

D3

0001

100

D4

0001

101

D5

0001

110

D6

0001

111

D7

Half word

0010

000

D0

D1

0010

001

D1

D2

0010

010

D2

D3

0010

011

D3

D4

0010

100

D4

D5

0010

101

D5

D6

0010

110

D6

D7

Tri-byte

0011

000

D0

D1

D2

0011

001

D1

D2

D3

0011

010

D2

D3

D4

0011

011

D3

D4

D5

0011

100

D4

D5

D6

0011

101

D5

D6

D7